# DEC 4000 AXP Model 600 Series

# **Technical Manual**

Order Number: EK-KN430-TM. A01

Digital Equipment Corporation Maynard, Massachusetts

#### First Printing, December 1992

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

© Digital Equipment Corporation 1992.

All rights reserved.

The following are trademarks of Digital Equipment Corporation: AXP, DEC, DEC VET, DECchip, OpenVMS, ULTRIX, VAX, VMS, the AXP logo, and the DIGITAL logo.

OSF/1 is a registered trademark of Open Software Foundation, Inc. All other trademarks and registered trademarks are the property of their respective holders.

S1757

This document was prepared with VAX DOCUMENT, Version 1.2.

# Contents

| Preface | xxxi |

|---------|------|

|         |      |

## Part I DEC 4000 System Description

## 1 DEC 4000 System Features

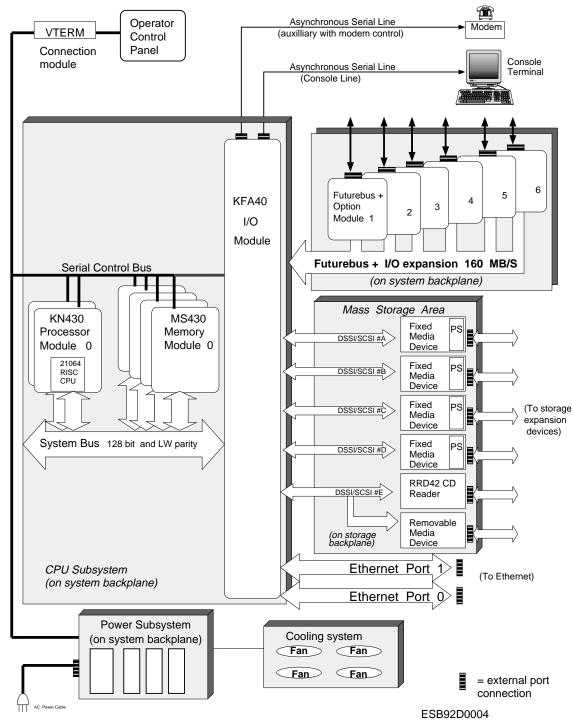

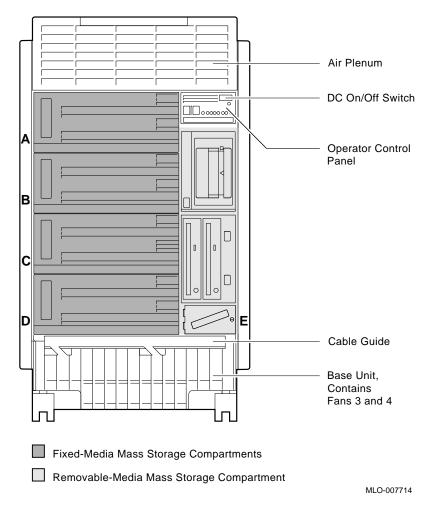

| 1.1 BA640 Cabinet                                        | 1–5  |

|----------------------------------------------------------|------|

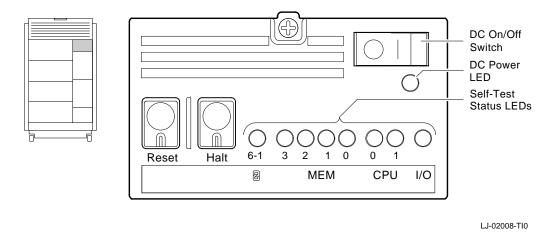

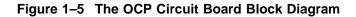

| 1.1.1 DC on/off Switch                                   | 1–8  |

| 1.1.2 RESET Switch                                       | 1–8  |

| 1.1.3 The Halt Switch                                    | 1–9  |

| 1.1.4 Power-up Console Baud rate switch                  | 1–9  |

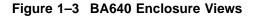

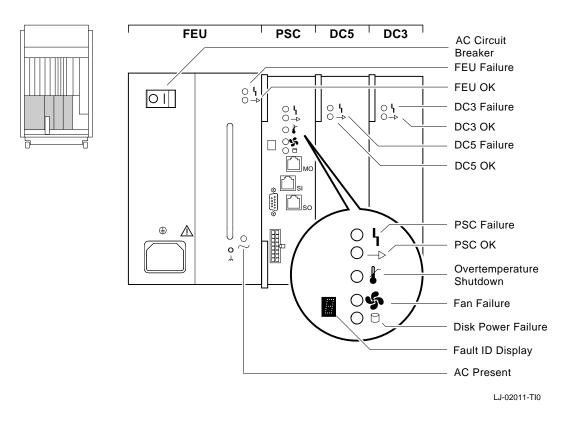

| 1.1.5 Status LEDs                                        | 1–10 |

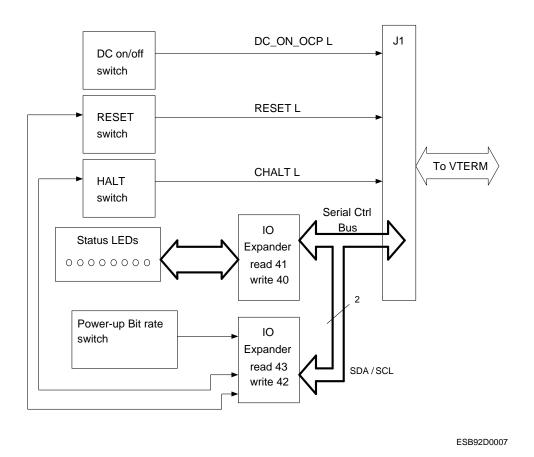

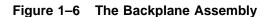

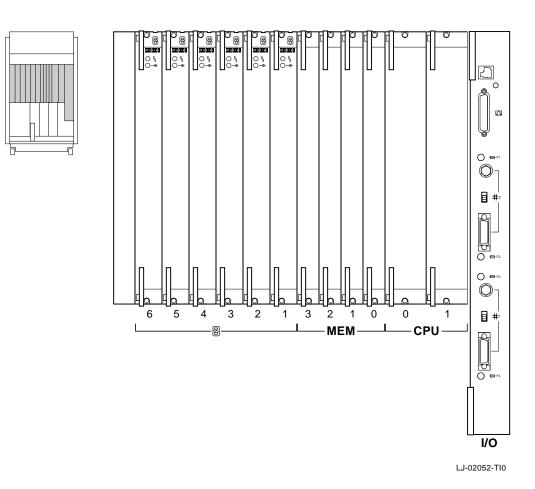

| 1.2 The Backplane Assembly                               | 1–10 |

| 1.2.1 The Storage Backplane Module                       | 1–11 |

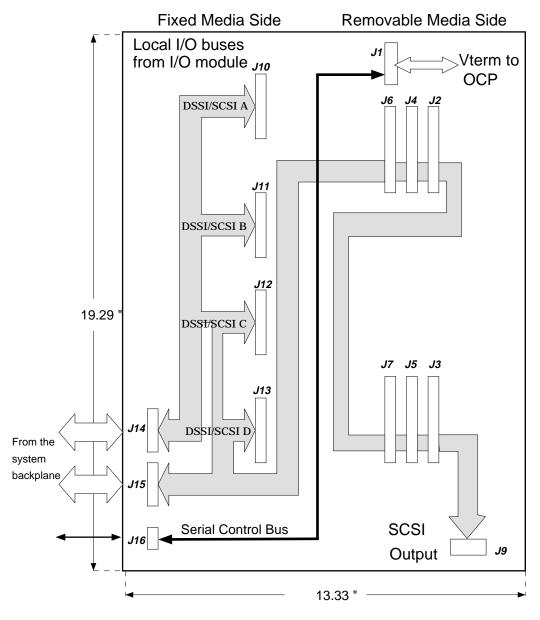

| 1.2.2 System Backplane Module                            | 1–13 |

| 1.2.3 System Bus Routing                                 | 1–13 |

| 1.2.4 Futurebus+ Routing                                 | 1–13 |

| 1.2.5 LocaL I/O Bus Routing                              | 1–13 |

| 1.2.6 Serial Control Bus Routing                         | 1–13 |

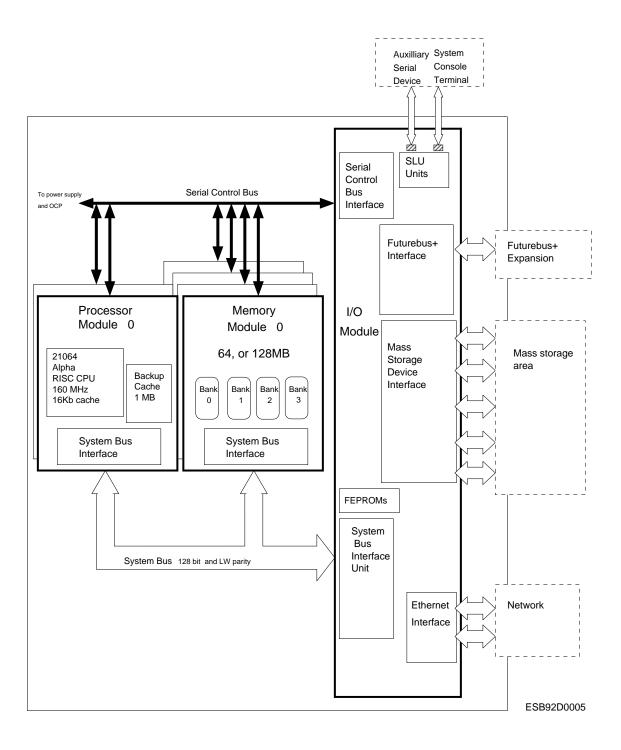

| 1.3 KN430 CPU Subsystem                                  | 1–14 |

| 1.3.1 Processor Module Differences                       | 1–14 |

| 1.3.2 Module order                                       | 1–17 |

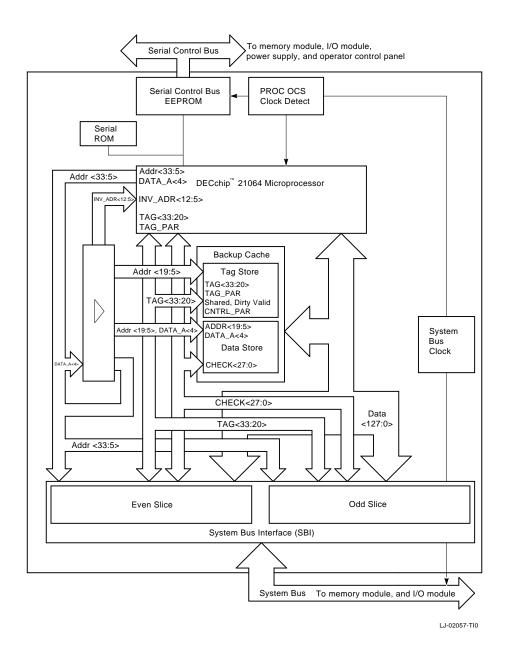

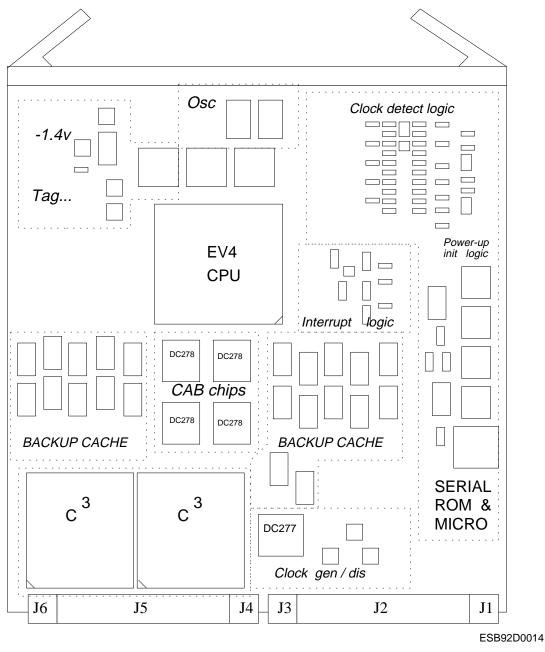

| 1.3.3 KN430 Processor Module                             | 1–17 |

| 1.3.3.1 Processor module components                      | 1–19 |

| 1.3.3.2 DECchip 21064 <sup>TM</sup> Alpha CPU            | 1–20 |

| 1.3.3.3Backup Cache Memory Devices                       | 1–21 |

| 1.3.3.4System bus interface                              | 1–21 |

| 1.3.3.5 System bus clock generator/distributor circuitry | 1–21 |

| 1.3.3.6Clock/ power detect circuit                       | 1–21 |

| 1.3.3.7Serial Control Bus Interface                      | 1–21 |

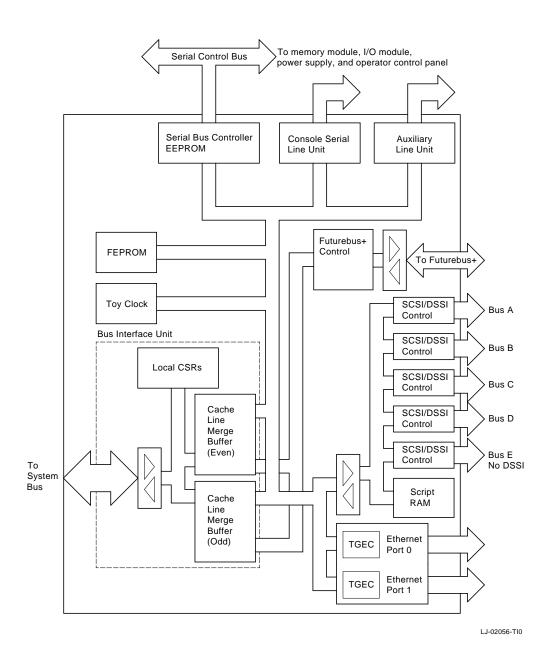

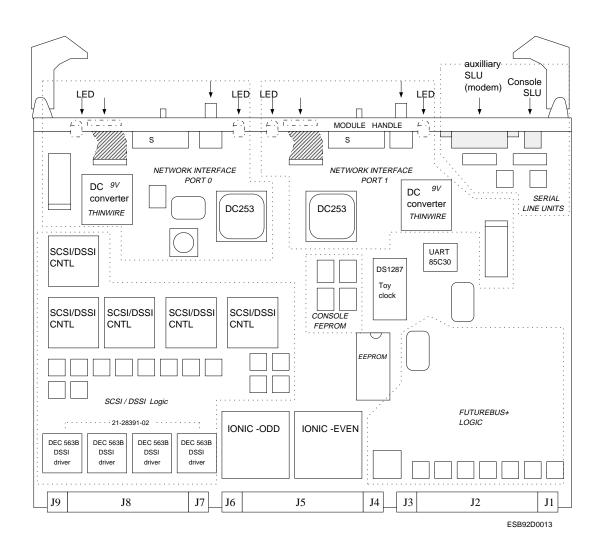

| 1.3.4 KFA40 I/O Module                                   | 1–22 |

| 1.3.4.1 EPROM                                            | 1–24 |

| 1.3.4.2 FEPROMS                                          | 1–24 |

| 1.3.4.3Ethernet Controllers                              | 1–24 |

| 1.3.4.4Serial Line Units                                 | 1–25 |

| 1.3.4.5 SCSI Controllers                                 | 1–25 |

| 1.3.4.6 IONIC gate arrays                                | 1–25 |

| 1.3.4.7         Time of Year Clock (TOY)                 | 1–25 |

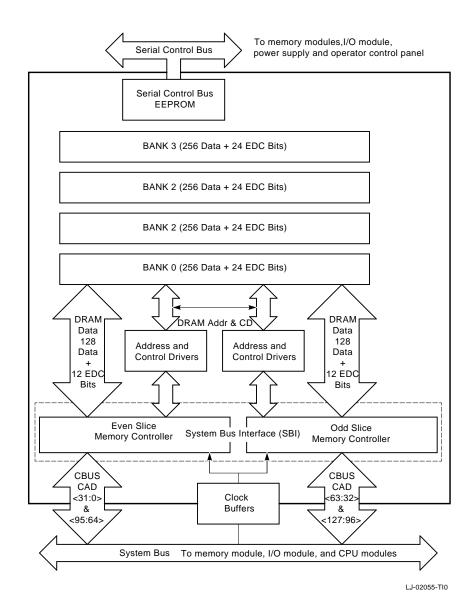

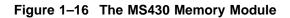

| 1.3.5         MS430 Memory Module                        | 1–26 |

| 1.3.5.1 DRAMS                                            | 1–28 |

| 1.3.5.2         Driver chips                             | 1–29 |

| 1.3.5.3         CMIC chips                               | 1–29 |

| 1.4   The System Bus                                     | 1–29 |

| 1.4.1Supported transactions                              | 1–29 |

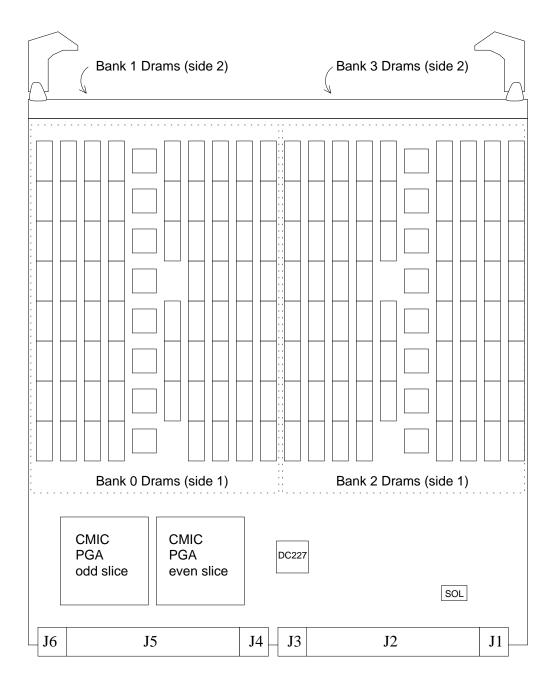

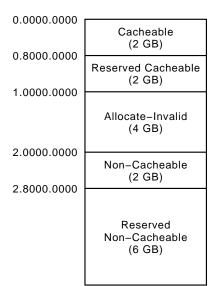

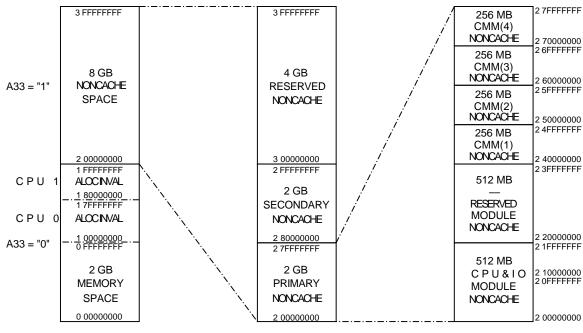

| 1.4.2  | Physical Address Space Layout                 | 1–32 |

|--------|-----------------------------------------------|------|

| 1.4.3  | System clock signals                          | 1–33 |

| 1.4.4  | Subsystem communications with secondary buses | 1–33 |

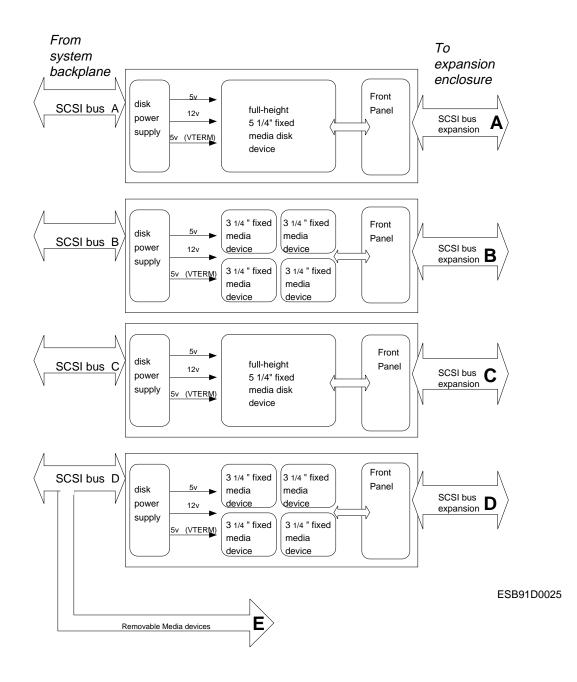

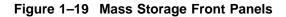

| 1.5    | The Mass Storage Area                         | 1–34 |

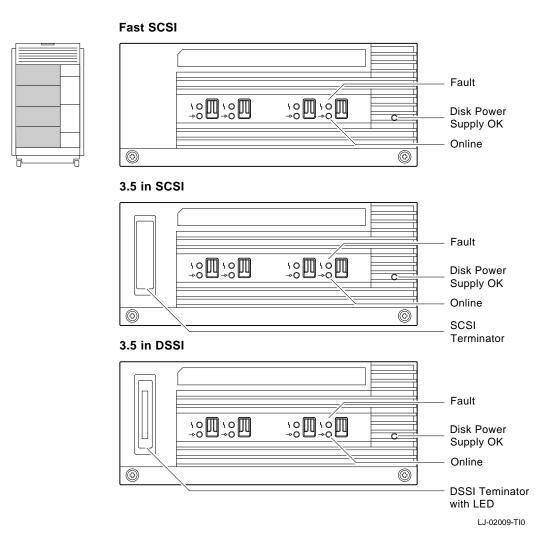

| 1.6    | I/O Expansion Area                            | 1–36 |

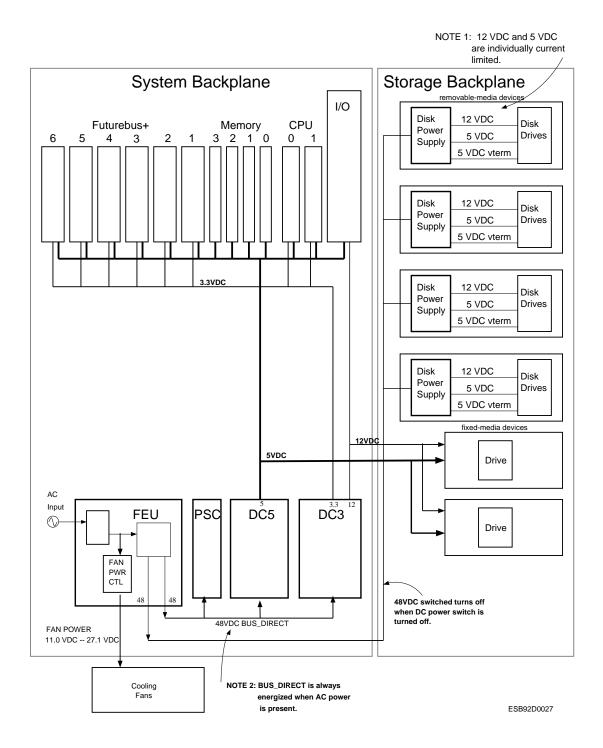

| 1.7    | The Power Supply Subsystem                    | 1–37 |

| 1.7.1  | H7853 Front End Unit (FEU)                    | 1–41 |

| 1.7.2  | H7851 Power System Controller (PSC)           | 1–41 |

| 1.7.3  | H7179 5 Volt Converter (DC5)                  | 1–42 |

| 1.7.4  | H7178 3 Volt Converter (DC3)                  | 1–42 |

| 1.7.5  | Disk Power Supplies                           | 1–42 |

| 1.7.6  | System Voltages                               | 1–42 |

| 1.8    | The Serial Control Bus                        | 1–43 |

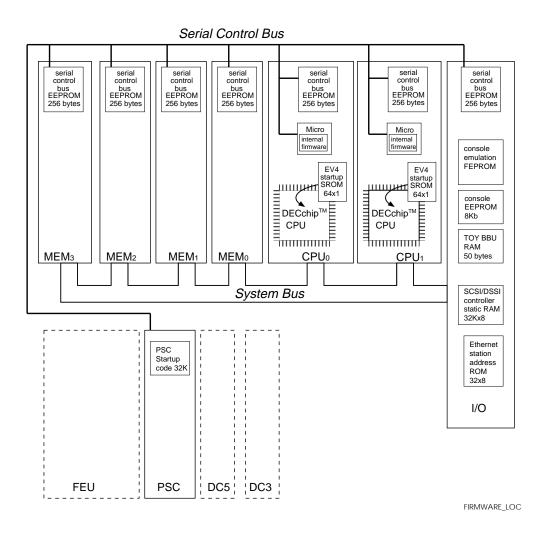

| 1.9    | System Firmware                               | 1–43 |

| 1.10   | System Ports                                  | 1–47 |

| 1.10.1 | The serial line ports (SLU)                   | 1–47 |

| 1.10.2 | The Ethernet Port                             | 1–48 |

| 1.10.3 | SCSI Storage Expansion Ports                  | 1–48 |

| 1.10.4 | AC Power Connector Port                       | 1–48 |

#### Part II The Processor Module

#### 2 The KN430 Processor Module

## 3 Alpha Architecture

| 3.1   | Addressing                         | 3–1  |

|-------|------------------------------------|------|

| 3.2   | Data Types                         | 3–1  |

| 3.3   | Alpha Registers                    | 3–11 |

| 3.3.1 | Program Counter Register           | 3–11 |

| 3.3.2 | Processor Status Register          | 3–11 |

| 3.3.3 | Integer Registers                  | 3–11 |

| 3.3.4 | Floating-point Registers           | 3–12 |

| 3.3.5 | Lock Registers                     | 3–12 |

| 3.3.6 | Alpha Internal Processor Registers | 3–12 |

| 3.3.7 | Optional Registers                 | 3–12 |

| 3.4   | Instruction Formats                | 3–12 |

# 4 The DECchip<sup>™</sup> 21064 CPU chip

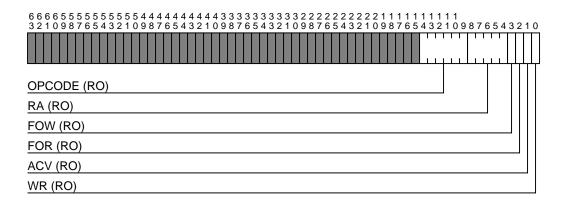

| 4.1    | I-box Internal Processor Registers                                 | 4–2  |

|--------|--------------------------------------------------------------------|------|

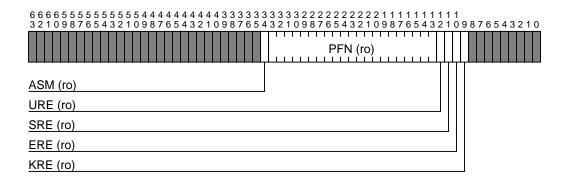

| 4.1.1  | Translation Buffer Tag Register (TB_TAG)                           | 4–2  |

| 4.1.2  | Instruction Translation Buffer Page Table Entry Register           |      |

|        | (ITB_PTE)                                                          | 4–3  |

| 4.1.3  | Instruction Cache Control and Status Register (ICCSR)              | 4–4  |

| 4.1.4  | Instruction Translation Buffer Page Table Entry Temporary Register |      |

|        | (ITB_PTE_TEMP)                                                     | 4–7  |

| 4.1.5  | Exception Address Register (EXC_ADDR)                              | 4–8  |

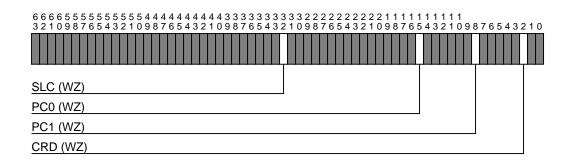

| 4.1.6  | Serial Line Clear Register (SL_CLR)                                | 4–9  |

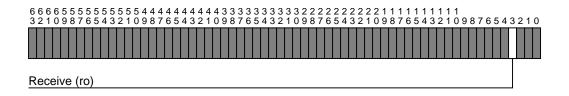

| 4.1.7  | Serial Line Receive Register (SL_RCV)                              | 4–10 |

| 4.1.8  | Instruction Translation Buffer Zap Register (ITBZAP)               | 4–10 |

| 4.1.9  | Instruction Translation Buffer ASM (ITBASM)                        | 4–10 |

| 4.1.10 | Instruction Translation Buffer IS Register (ITBIS)                 | 4–10 |

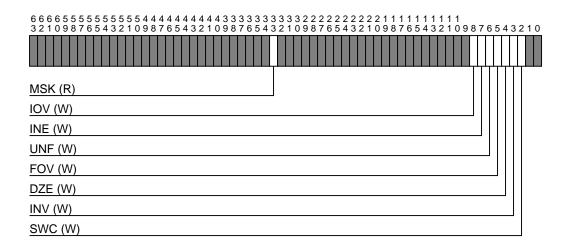

| 4.1.11 | Processor Status (PS)                                           | 4–11 |

|--------|-----------------------------------------------------------------|------|

| 4.1.12 | Exception Summary Register (EXC_SUM)                            | 4–11 |

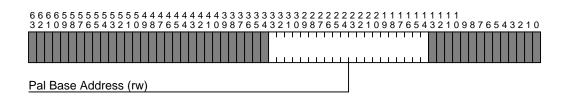

| 4.1.13 | Privileged Architecture Library Base Register (PAL_BASE)        | 4–13 |

| 4.1.14 | Hardware Interrupt Request Register (HIRR)                      | 4–13 |

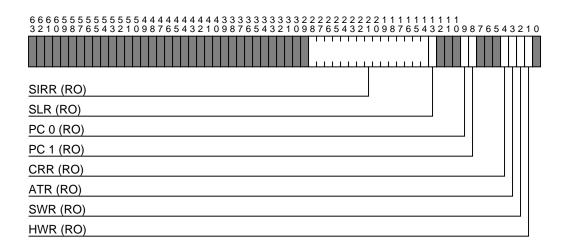

| 4.1.15 | Software Interrupt Request Register (SIRR)                      | 4–15 |

| 4.1.16 | Asynchronous Trap Request Register (ASTRR)                      | 4–15 |

| 4.1.17 | Hardware Interrupt Enable Register (HIER)                       | 4–16 |

| 4.1.18 | Software Interrupt Enable Register (SIER)                       | 4–17 |

| 4.1.19 | Asynchronous System Trap Enable Register (ASTER)                | 4–17 |

| 4.1.20 | Serial Line Transmit Register (SL_XMIT)                         | 4–18 |

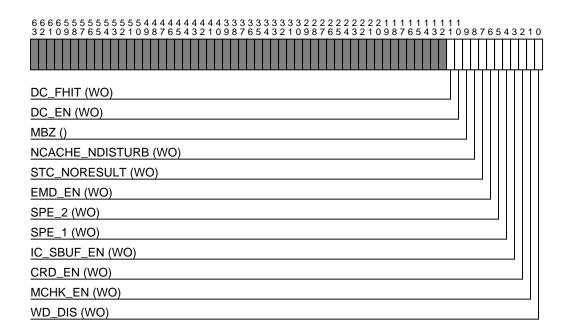

| 4.2    | A-box Internal Processor Registers                              | 4–19 |

| 4.2.1  | Translation Buffer Control Register (TB_CTL)                    | 4–19 |

| 4.2.2  | Data Translation Buffer Page Table Entry Register (TB_PTE)      | 4–19 |

| 4.2.3  | Data Translation Buffer Page Table Entry Temporary Register     |      |

|        | (DTB_PTE_TEMP)                                                  | 4–20 |

| 4.2.4  | Memory Management Control and Status Register (MM_CSR)          | 4–21 |

| 4.2.5  | Virtual Address Register(VA)                                    | 4–22 |

| 4.2.6  | Data Translation Buffer Zap Register (DTBZAP)                   | 4–22 |

| 4.2.7  | Data Translation Buffer ASM Register (DTBASM)                   | 4–22 |

| 4.2.8  | Data Translation Buffer Invalidate Signal Register (DTBIS)      | 4–22 |

| 4.2.9  | Flush Instruction Cache Register (FLUSH_IC)                     | 4–22 |

| 4.2.10 | Flush Instruction Cache ASM Register (FLUSH_IC_ASM)             | 4–22 |

| 4.2.11 | A-box Control Register (A-BOX_CTL)                              | 4–23 |

| 4.2.12 | Alternate Procssor Mode Register (ALT_MODE)                     | 4–24 |

| 4.2.13 | Cycle Counter Register                                          | 4–25 |

| 4.2.14 | Cycle Counter Control Register (CC_CTL)                         | 4–25 |

| 4.2.15 | Bus Interface Control Unit Register (BIU_CTL)                   | 4–26 |

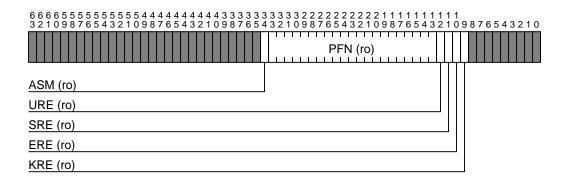

| 4.3    | Privileged Architecture Library Temporary Registers (PAL_TEMPs) | 4–28 |

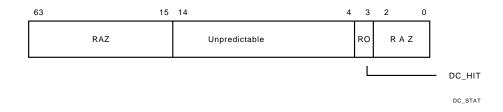

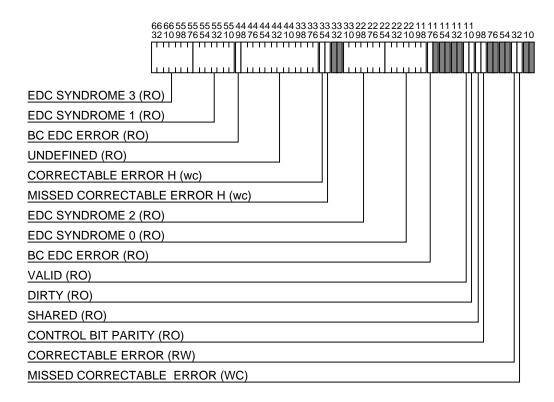

| 4.3.1  | Data Cache Status Register (DC_STAT)                            | 4–29 |

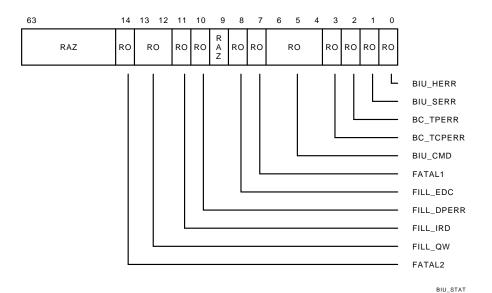

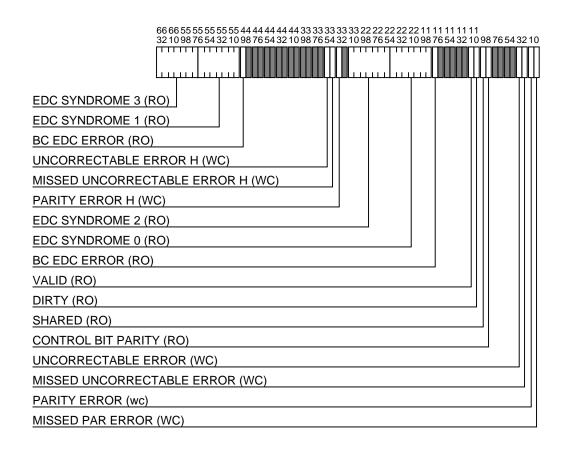

| 4.3.2  | Bus Interface Unit Status Register (BIU_STAT)                   | 4–31 |

| 4.3.3  | Bus Interface Unit Address Register (BIU_ADDR)                  | 4–32 |

| 4.3.4  | Fill Address Register (FILL_ADDR)                               | 4–33 |

| 4.3.5  | Fill Syndrome Register (FILL_SYNDROME)                          | 4–34 |

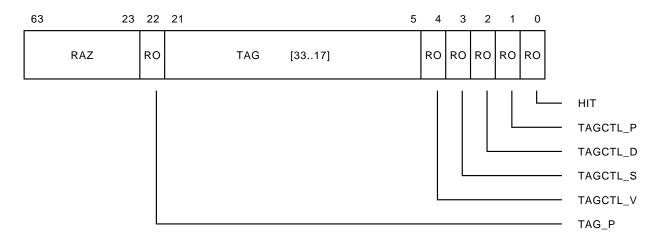

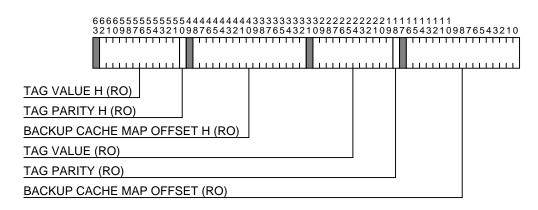

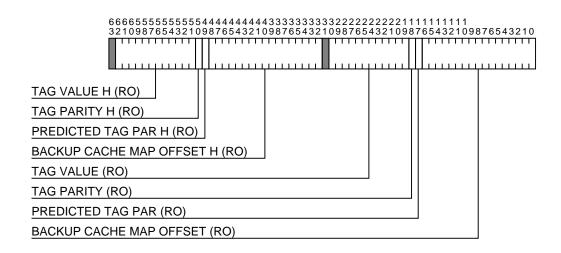

| 4.3.6  | Backup Cache Tag Register (BC_TAG)                              | 4–36 |

| 4.4    | Error Detection and Correction (EDC)                            | 4–37 |

# 5 Backup Cache (B-cache)

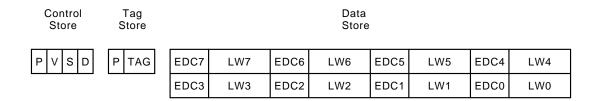

| 5.1   | Control Store                                                | 5–1  |

|-------|--------------------------------------------------------------|------|

| 5.2   | Tag Store                                                    | 5–2  |

| 5.3   | Data Store                                                   | 5–2  |

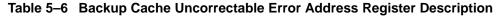

| 5.4   | Backup Cache Control Register Definitions                    | 5–3  |

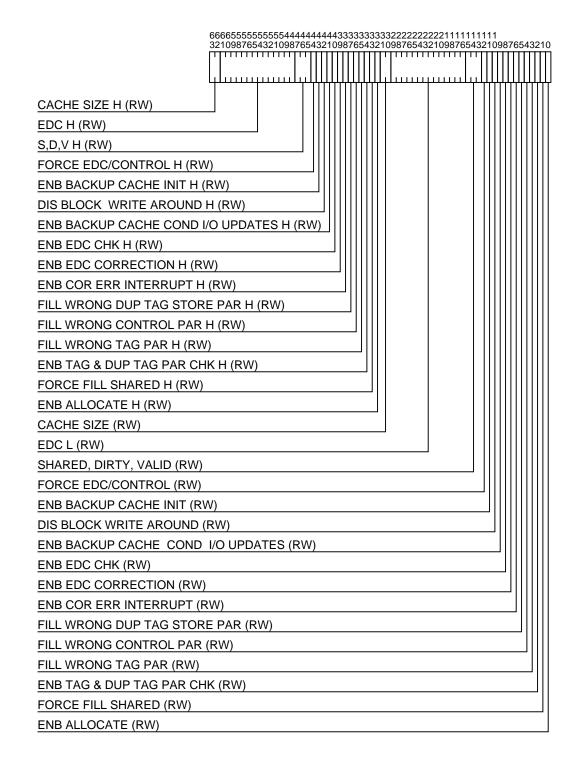

| 5.4.1 | Backup Cache Control Register (CSR0)                         | 5–3  |

| 5.4.2 | Backup Cache Correctable Error Register (CSR1)               | 5–8  |

| 5.4.3 | Backup Cache Correctable Error Address Register (BCCEA) CSR2 | 5–11 |

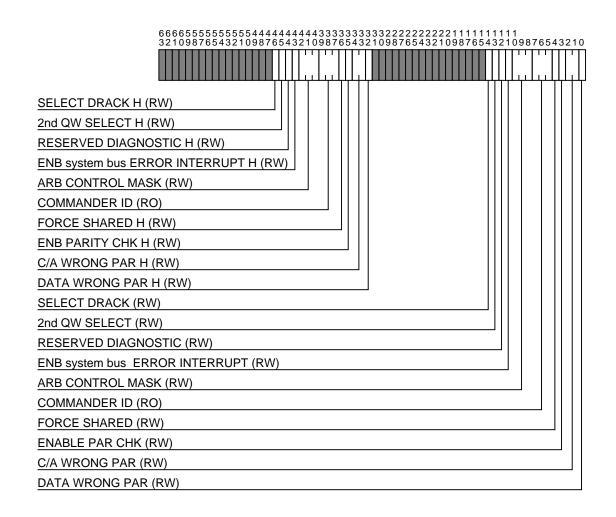

| 5.4.4 | Backup Cache Uncorrectable Error Register (CSR3)             | 5–12 |

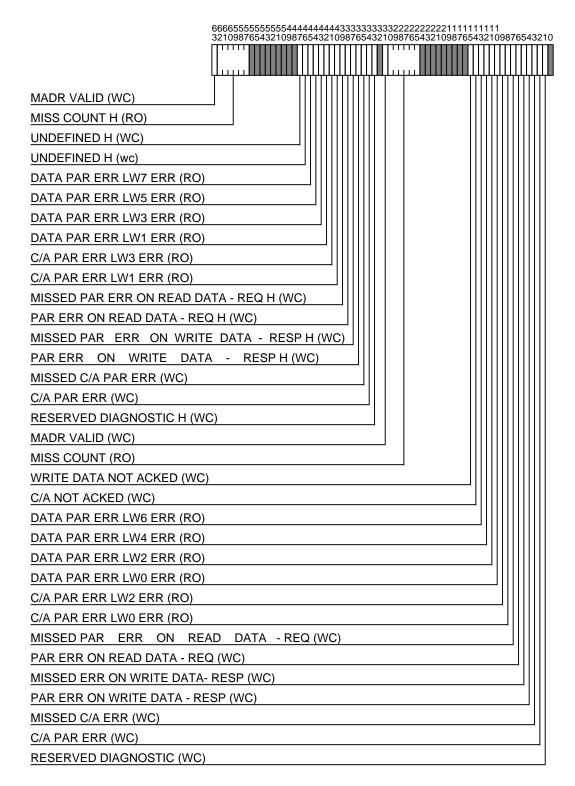

| 5.4.5 | Backup Cache Uncorrectable Error Address Register (CSR4)     | 5–15 |

| 5.4.6 | System Bus Cycles                                            | 5–17 |

| 5.5   | Cache Block Merge Buffer                                     | 5–17 |

| 5.6   | Duplicate Primary Data Cache Tag Store                       | 5–18 |

| 5.6.1 | Duplicate Tag Error Register (CSR5)                          | 5–20 |

| 5.7   | Lack of Duplicate Primary Instruction Cache Tag Store        | 5–22 |

| 5.8   | Lack of Cache Block Prefetch                                 | 5–22 |

| 5.9   | Data Integrity                                               | 5–22 |

## 6 System Bus Interface

| 6.1   | CPU System Bus Register Definitions               | 6–1  |

|-------|---------------------------------------------------|------|

| 6.1.1 | System Bus Control Register (CSR6)                | 6–1  |

| 6.1.2 | System Bus Error Register (CSR7)                  | 6–4  |

| 6.1.3 | System Bus Error Address Low Register (CSR8)      | 6–10 |

| 6.1.4 | System Bus Error Address High Register (CSR9)     | 6–11 |

| 6.2   | Multiprocessor Configuration CSR Definitions      | 6–13 |

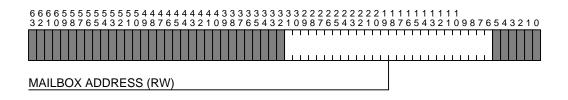

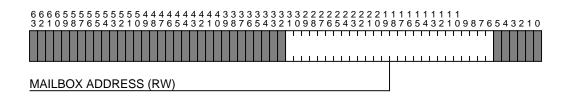

| 6.2.1 | Processor Mailbox Register (CSR10)                | 6–13 |

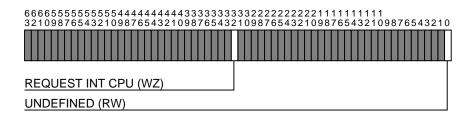

| 6.2.2 | Interprocessor Interrupt Request Register (CSR11) | 6–14 |

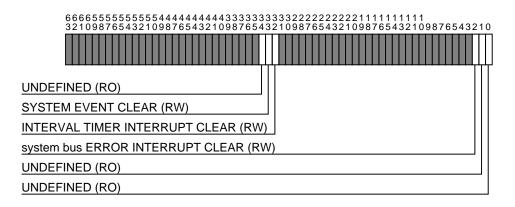

| 6.3   | System Interrupt Clear Register (CSR12)           | 6–14 |

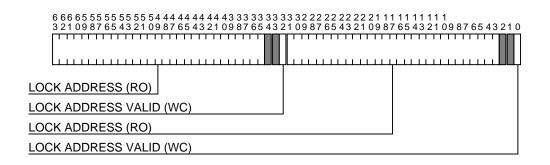

| 6.4   | Address Lock Register (CSR13)                     | 6–15 |

| 6.5   | Miss Address Register (CSR14)                     | 6–17 |

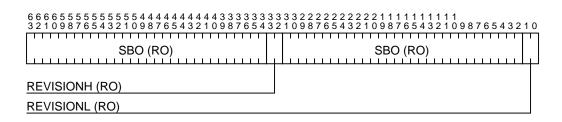

| 6.6   | C <sup>3</sup> Revision Register (CSR15)          | 6–18 |

| 6.7   | D-bus                                             | 6–19 |

| 6.8   | System Bus Arbiter                                | 6–22 |

| 6.9   | System Bus Clock Generator/Distributor            | 6–22 |

| 6.10  | System Bus CRESET L Generation                    | 6–22 |

| 6.11  | OCP Halt Request Buffer                           | 6–23 |

| 6.12  | Nonvolatile EEPROM                                | 6–23 |

## 7 CPU Module Transactions

| 7.1     | Processor Transactions                               | 7–1  |

|---------|------------------------------------------------------|------|

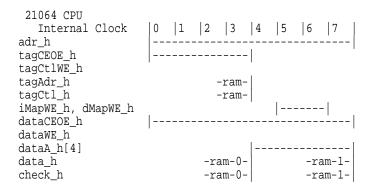

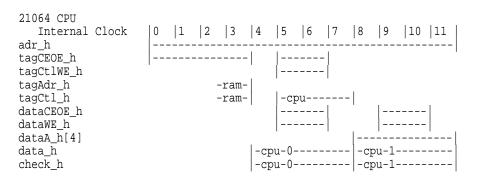

| 7.1.1   | 21064 CPU Chip Transactions                          | 7–2  |

| 7.1.1.1 | Fast External Cache Read Hit                         | 7–3  |

| 7.1.1.2 | Fast External Cache Write Hit                        | 7–3  |

| 7.1.1.3 | READ_BLOCK                                           | 7–4  |

| 7.1.1.4 | Write_block                                          | 7–5  |

| 7.1.1.5 | LDxL                                                 | 7–6  |

| 7.1.1.6 | STxC                                                 | 7–6  |

| 7.1.1.7 | BARRIER                                              | 7–6  |

| 7.1.1.8 | FETCH                                                | 7–7  |

| 7.1.1.9 | FETCHM                                               | 7–7  |

| 7.1.2   | Cacheable versus Non-Cacheable, and Allocate-Invalid | 7–7  |

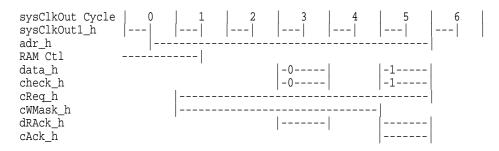

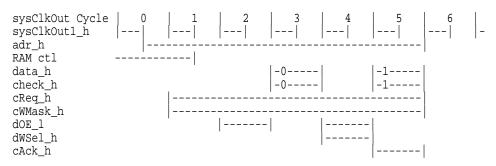

| 7.2     | System Bus Transactions                              | 7–9  |

| 7.2.1   | CPU as Commander                                     | 7–10 |

| 7.2.2   | CPU as Bystander                                     | 7–10 |

| 7.2.3   | CPU as Responder                                     | 7–10 |

| 7.3     | Control Flow of CPU Module Transactions              | 7–10 |

| 7.3.1   | Processor Initiated Transactions                     | 7–10 |

| 7.3.2   | System Bus Initiated Transactions                    | 7–15 |

# 8 Cache Invalidate Management

| 8.1 | Processor Caused Invalidates  | 8–1 |

|-----|-------------------------------|-----|

| 8.2 | System Bus Caused Invalidates | 8–1 |

## 9 Exceptions and Interrupts

| 9.1 Pro    | ocessor-Generated Interrupts                 | 9–1  |

|------------|----------------------------------------------|------|

| 9.1.1      | Exception Handling                           | 9–2  |

| 9.1.1.1    | PAL Priority Level                           | 9–3  |

| 9.1.1.2    | PALcode 0020 Entry Characteristics           | 9–3  |

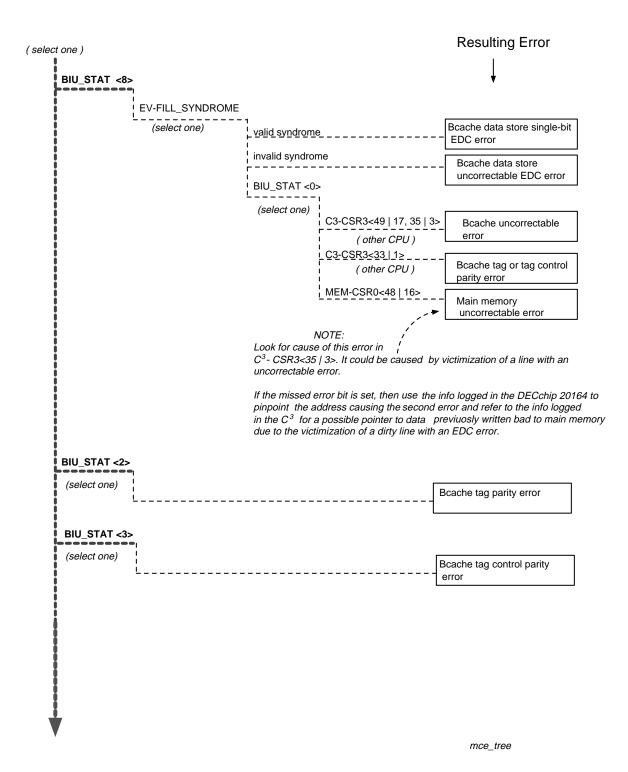

| 9.1.1.3    | Parse Tree PALcode Entry 0020 <sub>16</sub>  | 9–3  |

| 9.1.1.4    | PAL Routine Behavior                         | 9–7  |

| 9.1.1.4.1  | Backup Cache Tag Parity Error                | 9–7  |

| 9.1.1.4.2  | Backup Cache Tag Control Parity Error        | 9–7  |

| 9.1.1.4.3  | Backup Cache Data Single Bit EDC Error       | 9–7  |

| 9.1.1.4.4  | Backup Cache Data Uncorrectable EDC Error    | 9–7  |

| 9.1.1.4.5  | Backup Cache Data Single Bit EDC Error       | 9–8  |

| 9.1.1.4.6  | Backup Cache Data Uncorrectable EDC Error    | 9–8  |

| 9.1.1.4.7  | 21064 Data Bus Single-bit EDC Error          | 9–8  |

| 9.1.1.4.8  | 21064 Data Bus Uncorrectable EDC Error       | 9–8  |

| 9.1.1.4.9  | Backup Cache Tag or Tag Control Parity Error | 9–8  |

| 9.1.1.4.10 | System Bus Parity Error                      | 9–9  |

| 9.1.1.4.11 | Invalid System Bus Address                   | 9–9  |

| 9.1.1.4.12 | Other CPU Errors                             | 9–9  |

| 9.1.1.4.13 | Main Memory Uncorrectable EDC Errors         | 9–9  |

| 9.2 No     | n-processor Generated Interrupts             | 9–9  |

| 9.2.1      | Interrupt Handling                           | 9–10 |

| 9.2.1.1    | PAL Priority Level                           | 9–10 |

| 9.2.1.2    | PALcode 00E0 Entry Characteristics           | 9–10 |

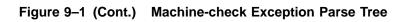

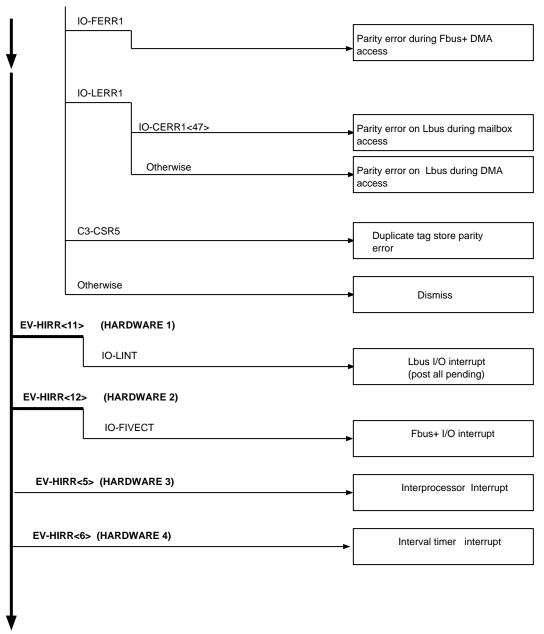

| 9.2.1.3    | Parse Tree PALcode Entry 00E0 <sub>16</sub>  | 9–11 |

| 9.2.1.4    | Hardware 0 Hardware Error                    | 9–15 |

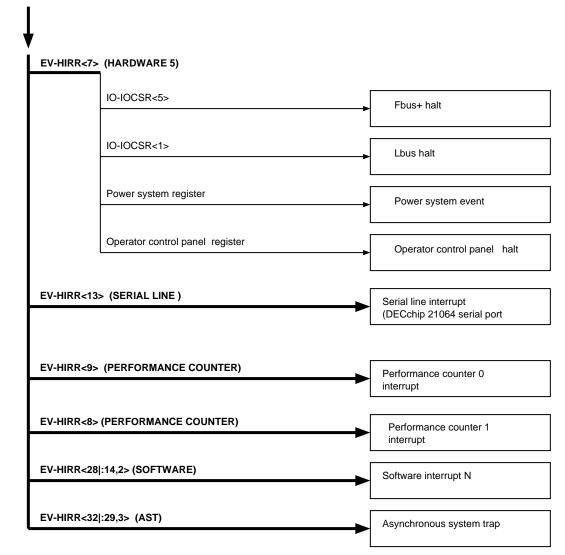

| 9.2.1.5    | Hardware 1 Local I/O                         | 9–17 |

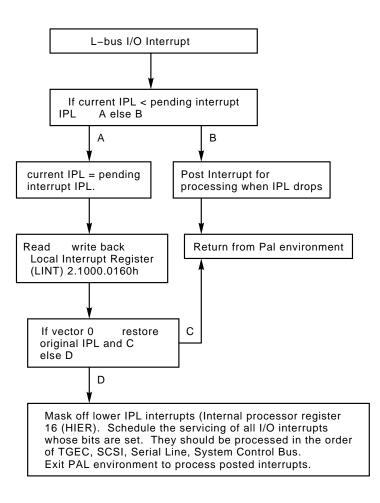

| 9.2.1.6    | Hardware 2 Futurebus+                        | 9–18 |

| 9.2.1.7    | Hardware 3 Interprocessor                    | 9–19 |

| 9.2.1.8    | Hardware 4 Interval Timer                    | 9–19 |

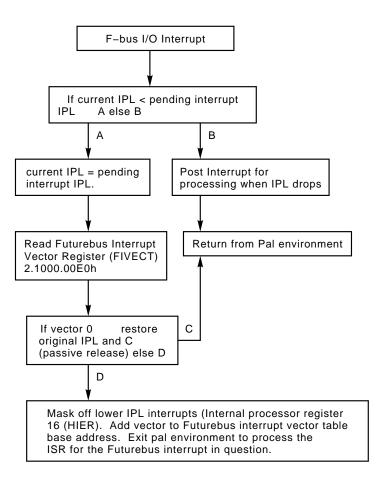

| 9.2.1.9    | Hardware 5 System Events                     | 9–20 |

| 9.2.1.10   | Software X Interrupt                         | 9–20 |

| 9.2.1.11   | Serial Line Interrupt                        | 9–20 |

| 9.2.1.12   | Asynchronous System Trap Interrupt           | 9–20 |

## 10 Fault Management and Error Recovery

| 10.1 Processor Errors                                | 10–1 |

|------------------------------------------------------|------|

| 10.2 Backup Cache Errors                             | 10–1 |

| 10.2.1 Tag and Tag Control Store Parity Errors       | 10–1 |

| 10.2.2 Data Store EDC Errors                         | 10–3 |

| 10.2.2.1 Correctable                                 | 10–3 |

| 10.2.2.2 Uncorrectable Errors                        | 10–6 |

| 10.3 Duplicate Primary Cache Tag Store Parity Errors | 10–8 |

| 10.4 System Bus Errors                               | 10–9 |

| 10.4.1 C/A Parity Error                              | 10–9 |

| 10.4.2 Data Parity Error                             | 10–9 |

| 10.4.3 Invalid Address - Bus Time-out 10             | 0–10 |

| 10.5         I/O Subsystem Errors         10         | 0–10 |

| 10.6         C_ERR L Assertion         10            | 0–10 |

## 11 CPU Power-Up and Initialization

| 11.1   | Internal Processor Registers and the Internal JSR Stack | 11–1 |

|--------|---------------------------------------------------------|------|

| 11.2   | Backup Cache Initialization                             | 11–1 |

| 11.2.1 | LDQ Data Format, BCC ENABLE BACKUP CACHE INIT Set       | 11–2 |

| 11.3   | Duplicate Tag Store Initialization                      | 11–3 |

| 11.4   | System Bus Interface Initialization                     | 11–3 |

| 11.5   | CPU Clocks and Reset                                    | 11–3 |

| 11.6   | Power-Up Sequence                                       | 11–3 |

| 11.7   | Powering Up with Bad Main Memory                        | 11–3 |

## Part III The I/O Module

#### 12 The KFA40 I/O Module

#### 13 Address Mapping

| 13.1  | System Memory Space                           | 13–1  |

|-------|-----------------------------------------------|-------|

| 13.2  | Primary I/O Space                             | 13–2  |

| 13.3  | Diagnostic Mode Address Registers             | 13–5  |

| 13.4  | I/O Control/Status Register (IOCSR)           | 13–6  |

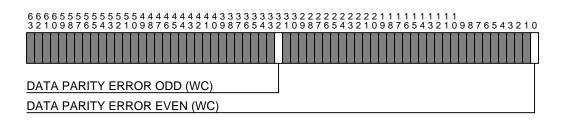

| 13.5  | System Bus Error Register 1 (CERR1)           | 13–11 |

| 13.6  | System Bus Error Register 2 (CERR2)           | 13–17 |

| 13.7  | System Bus Error Register 3 (CERR3)           | 13–18 |

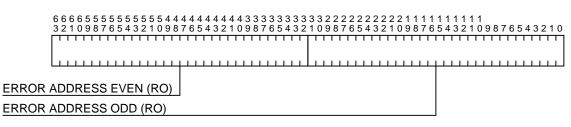

| 13.8  | Lbus Mailbox Pointer Register (LMBPR)         | 13–18 |

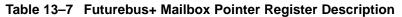

| 13.9  | Futurebus+ Mailbox Pointer Register (FMBPR)   | 13–19 |

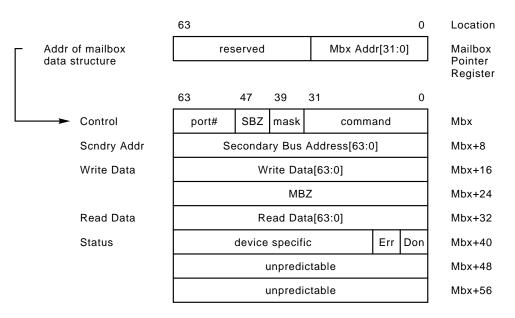

| 13.10 | Diagnostic Control/Status Register (DIAGCSR)  | 13–20 |

| 13.11 | Futurebus+ Interrupt Vector Register (FIVECT) | 13–21 |

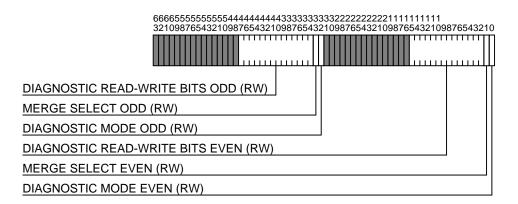

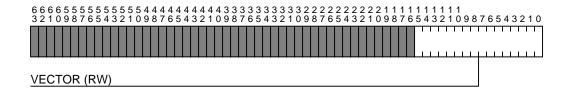

| 13.12 | Futurebus Halt Vector Register (FHVECT)       | 13–22 |

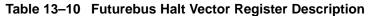

| 13.13 | Futurebus Error Register 1 (FERR1)            | 13–22 |

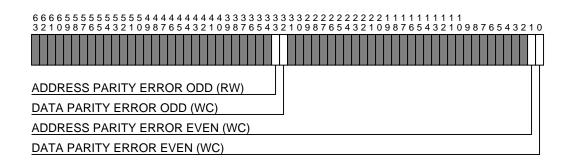

| 13.14 |                                               | 13–23 |

| 13.15 | Local Interrupt Register (LINT)               | 13–24 |

| 13.16 |                                               | 13–26 |

| 13.17 |                                               | 13–27 |

| 13.18 |                                               | 13–28 |

| 13.18 |                                               | 13–28 |

| 13.18 | .2 Software-visible Control Flow              | 13–29 |

| 13.18 | .3 Mailbox Pointer Registers                  | 13–29 |

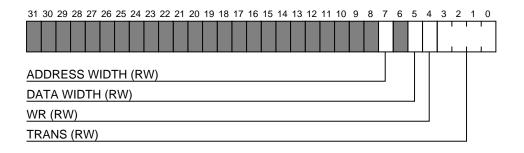

| 13.18 | .4 Mailbox Operation                          | 13–36 |

|       |                                               |       |

## 14 Interrupts

| 14.1 | Futurebus+ Interrupts           | 14–1 |

|------|---------------------------------|------|

|      | Local I/O Interrupts            |      |

|      | Hardware Error Interrupts       |      |

|      | System Event Interrupt Requests |      |

## 15 Futurebus+ Adapter Architecture

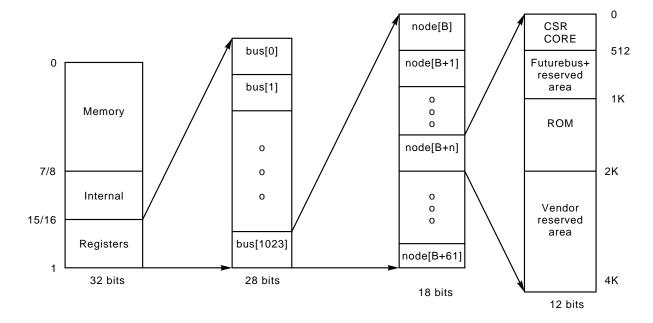

| 15.1   | Futurebus+ Address Space                     | 15–1 |

|--------|----------------------------------------------|------|

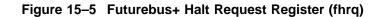

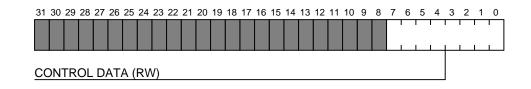

| 15.2   | Futurebus+ Adapter Registers                 | 15–3 |

|        | Futurebus+ Interrupt Request Register (FIRQ) |      |

|        | Futurebus+ Halt Request Register (FHRQ)      |      |

| 15.5   | Supported Data Transfer Protocols            |      |

| 15.5.1 | Futurebus+ Slave                             | 15–5 |

| 15.5.2 | Futurebus+ Master                            | 15–5 |

| 15.6   | Futurebus+ Error Handling                    | 15–6 |

#### 16 Local I/O Devices

| 16.1  | Lbus Addressing                     | 16–1  |

|-------|-------------------------------------|-------|

| 16.2  | EEPROM                              | 16–2  |

| 16.3  | Serial Line Ports                   | 16–2  |

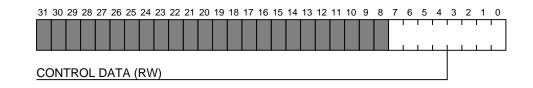

| 16.4  | AUX_CTRL Register (ACR)             | 16–4  |

| 16.5  | AUX_Data Register (AD)              | 16–4  |

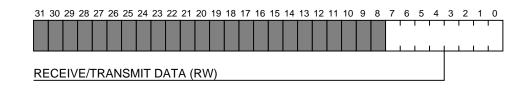

| 16.6  | Console Control Register (CON_CTRL) | 16–5  |

| 16.7  | Console Data Register (CD)          | 16–5  |

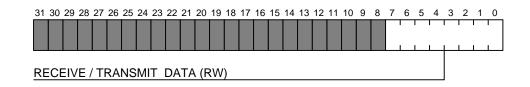

| 16.8  | Time-of-Year Clock (TOY)            | 16–6  |

| 16.9  | TOY Register A (TOYA)               | 16–7  |

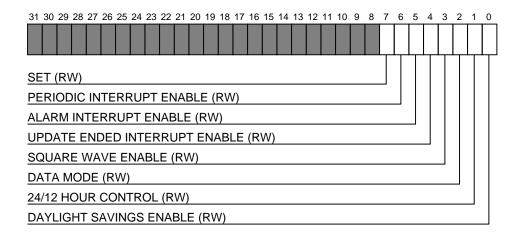

| 16.10 | TOY Register B (TOYB)               | 16–9  |

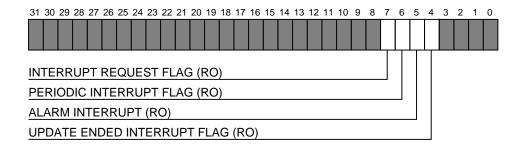

| 16.11 | TOY Register C (TOYC)               | 16–11 |

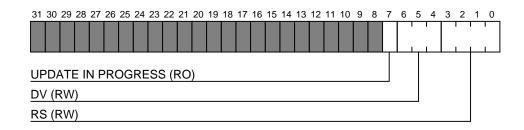

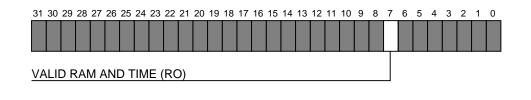

| 16.12 | TOY Register D (TOYD)               | 16–12 |

## 17 Ethernet Adapters (TGEC)

| 17.1 TC    | EC Programming                                     | 17–2  |

|------------|----------------------------------------------------|-------|

| 17.1.1     | Programming Overview                               | 17–2  |

| 17.1.2     | TGEC Command and Status Registers                  | 17–3  |

| 17.1.3     | Host Access to CSRs                                | 17–3  |

| 17.1.3.1   | TGEC Physical CSRs                                 | 17–4  |

| 17.1.3.2   | TGEC Virtual CSRs                                  | 17–4  |

| 17.1.3.2.1 | CSR Write                                          | 17–4  |

| 17.1.3.2.2 | CSR Read                                           | 17–4  |

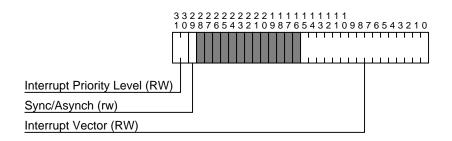

| 17.1.4     | Vector Address, IPL, Sync/Asynch (CSR0)            | 17–5  |

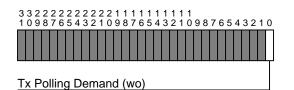

| 17.1.5     | Transmit Polling Demand (CSR1)                     | 17–7  |

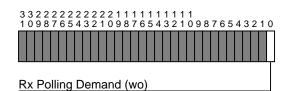

| 17.1.6     | Receive Polling Demand (CSR2)                      | 17–8  |

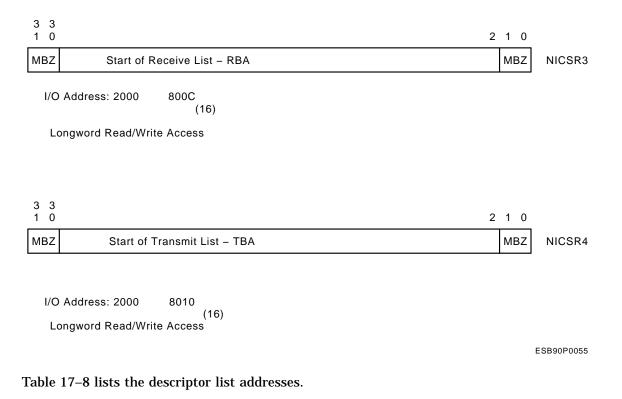

| 17.1.7     | Descriptor List Addresses (CSR3, CSR4)             | 17–9  |

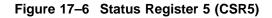

| 17.1.8     | Status Register (CSR5)                             | 17–12 |

| 17.1.8.1   | CSR5 Status Report                                 | 17–15 |

| 17.1.9     | Command and Mode Register (CSR6)                   | 17–17 |

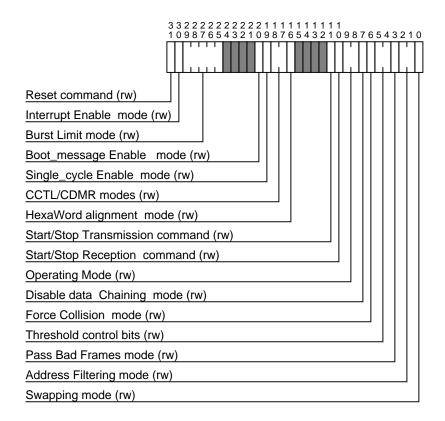

| 17.1.10    | System Base Register (CSR7)                        | 17–22 |

| 17.1.11    | Reserved Register (CSR8)                           | 17–23 |

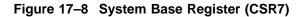

| 17.1.12    | Watchdog Timers (CSR9)                             | 17–23 |

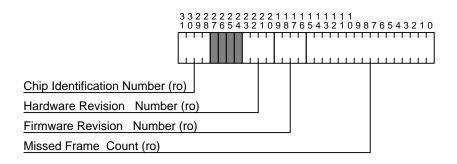

| 17.1.13    | TGEC Identification and Missed Frame Count (CSR10) | 17–25 |

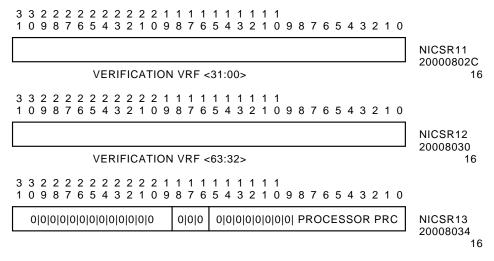

| 17.1.14    | Boot Message (CSR11, 12, 13)                       | 17–26 |

| 17.1.15    | Diagnostic Registers (CSR14, 15)                   | 17–28 |

| 17.2 De    | scriptors and Buffers Format                       | 17–28 |

|            |                                                    |       |

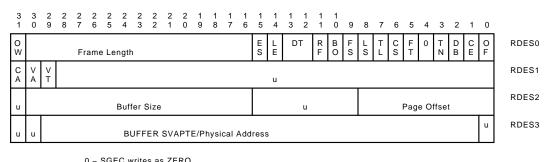

| 17.2.1   | Receive Descriptors                     | 17–28 |

|----------|-----------------------------------------|-------|

| 17.2.1.1 | RDES0 Word                              | 17–29 |

| 17.2.1.2 | RDES1 Word                              | 17–31 |

| 17.2.1.3 | RDES2 Word                              | 17–32 |

| 17.2.1.4 | RDES3 Word                              | 17–32 |

| 17.2.1.5 | Receive Descriptor Status Validity      | 17–33 |

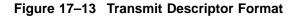

| 17.2.2   | Transmit Descriptors                    | 17–33 |

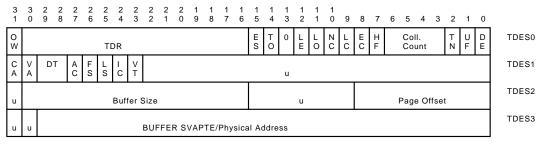

| 17.2.2.1 | TDES0 Word                              | 17–34 |

| 17.2.2.2 | TDES1 word                              | 17–35 |

| 17.2.2.3 | TDES2 Word                              | 17–37 |

| 17.2.2.4 | TDES3 word                              | 17–37 |

| 17.2.2.5 | Transmit Descriptor Status Validity     | 17–37 |

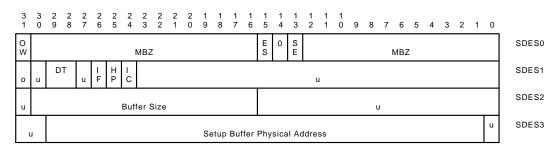

| 17.2.3   | Setup Frame                             | 17–38 |

| 17.2.3.1 | First Setup Frame                       | 17–38 |

| 17.2.3.2 | Subsequent Setup Frame                  | 17–38 |

| 17.2.3.3 | Setup Frame Descriptor                  | 17–38 |

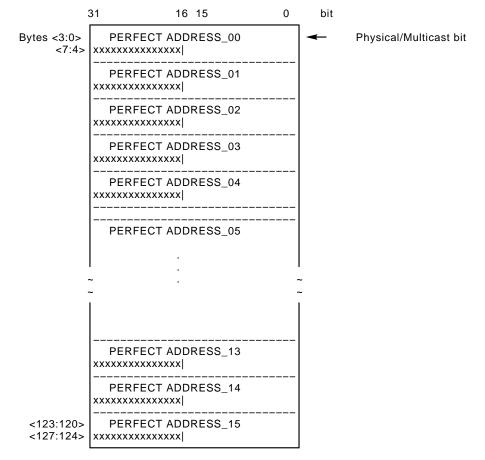

| 17.2.3.4 | Perfect Filtering Setup Frame Buffer    | 17–40 |

| 17.2.3.5 | Imperfect Filtering Setup Frame Buffer  | 17–42 |

|          | EC Hardware and Software Reset          | 17–44 |

|          | EC Interrupts                           | 17–45 |

| 17.4.1   | Startup Procedure                       | 17–46 |

| 17.5 Ree | ception Process                         | 17–46 |

| 17.5.1   | Transmission Process                    | 17–48 |

| 17.5.2   | Loopback Operations                     | 17–50 |

| 17.5.3   | DNA CSMA/CD Counters and Events Support | 17–51 |

## 18 SCSI/DSSI Adapters

| NCR 53C710 SCSI Adapter Registers | 18–1                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCSI Register Map                 | 18–2                                                                                                                                                                                                                                                                                                                                        |

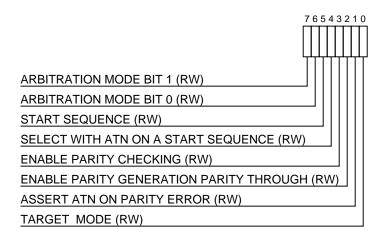

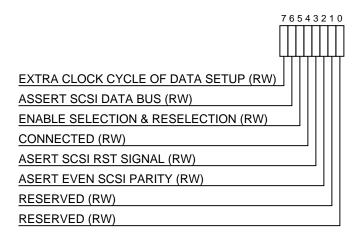

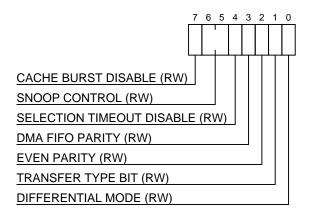

| SCSI Control 0 (SCNTL0)           | 18–4                                                                                                                                                                                                                                                                                                                                        |

| SCSI Control 1 (SCNTL1)           | 18–6                                                                                                                                                                                                                                                                                                                                        |

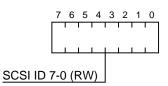

| SCSI Destination ID (SDID)        | 18–8                                                                                                                                                                                                                                                                                                                                        |

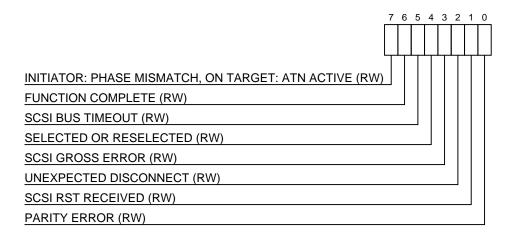

| SCSI Interrupt Enable (SIEN)      | 18–8                                                                                                                                                                                                                                                                                                                                        |

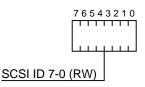

| SCSI Chip ID (SCID)               | 18–9                                                                                                                                                                                                                                                                                                                                        |

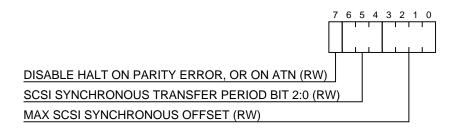

| SCSI Transfer (SXFER)             | 18–10                                                                                                                                                                                                                                                                                                                                       |

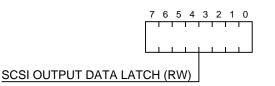

| SCSI Output Data Latch (SODL)     | 18–13                                                                                                                                                                                                                                                                                                                                       |

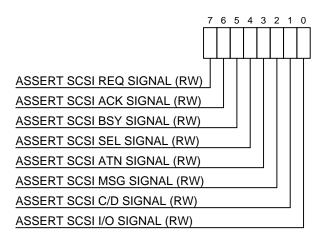

| SCSI Output Control Latch (SOCL)  | 18–13                                                                                                                                                                                                                                                                                                                                       |

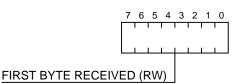

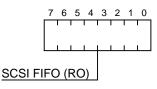

|                                   | 18–14                                                                                                                                                                                                                                                                                                                                       |

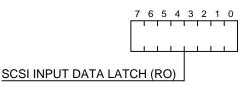

| SCSI Input Data Latch (SIDL)      | 18–15                                                                                                                                                                                                                                                                                                                                       |

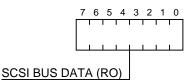

|                                   | 18–16                                                                                                                                                                                                                                                                                                                                       |

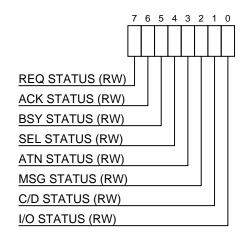

| SCSI Bus Control Lines (SBCL)     | 18–16                                                                                                                                                                                                                                                                                                                                       |

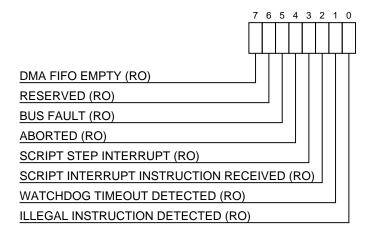

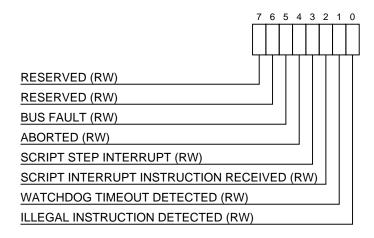

| DMA Status (DSTAT)                | 18–17                                                                                                                                                                                                                                                                                                                                       |

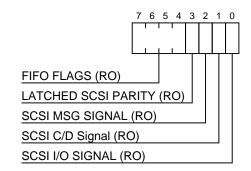

| SCSI Status Zero (SSTATO)         | 18–19                                                                                                                                                                                                                                                                                                                                       |

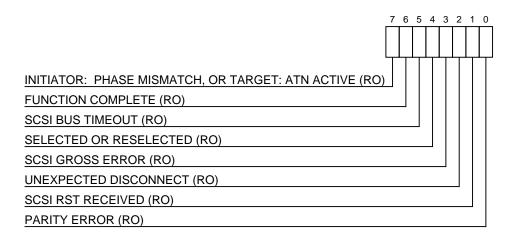

|                                   | 18–21                                                                                                                                                                                                                                                                                                                                       |

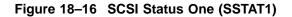

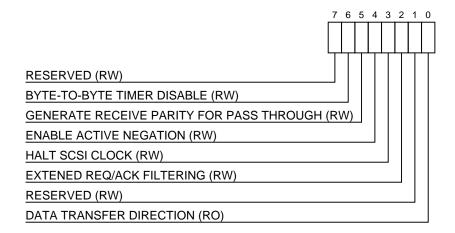

|                                   | 18–22                                                                                                                                                                                                                                                                                                                                       |

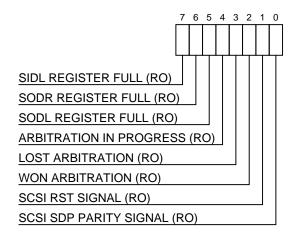

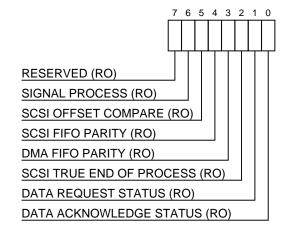

|                                   | 18–23                                                                                                                                                                                                                                                                                                                                       |

| Chip Test Zero (CTEST0)           | 18–24                                                                                                                                                                                                                                                                                                                                       |

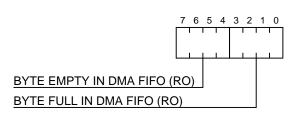

| Chip Test One (CTEST1)            | 18–25                                                                                                                                                                                                                                                                                                                                       |

| Chip Test Two (CTEST2)            | 18–26                                                                                                                                                                                                                                                                                                                                       |

| Chip Test Three (CTEST3)          | 18–27                                                                                                                                                                                                                                                                                                                                       |

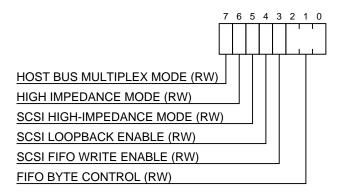

| Chip Test Four (CTEST4)           | 18–28                                                                                                                                                                                                                                                                                                                                       |

| Chip Test Five (CTEST5)           | 18–29                                                                                                                                                                                                                                                                                                                                       |

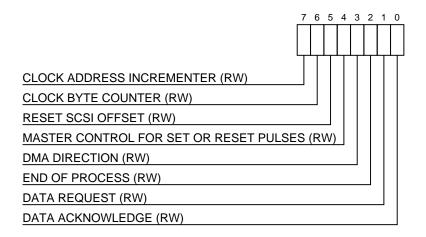

| Chip Test Six (CTEST6)            | 18–31                                                                                                                                                                                                                                                                                                                                       |

|                                   | SCSI Register MapSCSI Control 0 (SCNTL0)SCSI Control 1 (SCNTL1)SCSI Destination ID (SDID)SCSI Interrupt Enable (SIEN)SCSI Chip ID (SCID)SCSI Transfer (SXFER)SCSI Output Data Latch (SODL)SCSI Output Control Latch (SOCL)SCSI First Byte Received (SFBR)SCSI Input Data Latch (SIDL)SCSI Input Data Latch (SIDL)SCSI Bus Data Lines (SBDL) |

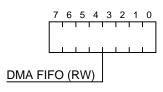

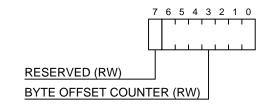

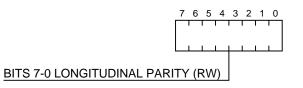

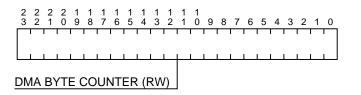

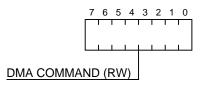

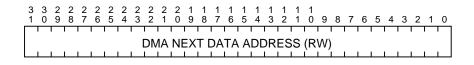

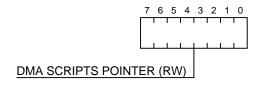

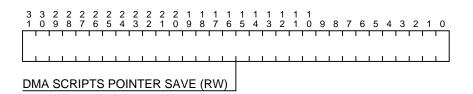

| 18.26       Chip Test Seven (CTEST7)       18–32         18.27       Temporary Stack (TEMP)       18–33         18.28       DMA FIFO (DFIFO)       18–33         18.29       Interrupt Status (ISTAT)       18–33         18.30       Chip Test Eight (CTEST8)       18–33         18.31       Longitudinal Parity (LCRC)       18–33         18.32       DMA Byte Counter (DBC)       18–33         18.33       DMA Command (DCMD)       18–33         18.34       DMA Next Data Address (DNAD)       18–40         18.35       DMA Scripts Pointer (DSP)       18–40         18.36       DMA Scripts Pointer Save (DSPS)       18–41         18.38       DMA Mode (DMODE)       18–42         18.39       DMA Interrupt Enable (DIEN)       18–42         18.40       DMA Watchdog Timer (DWT)       18–42         18.41       DMA Control Register (DCNTL)       18–44         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47         18.42.2       Ethernet Station Address ROM       18–47 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18.28       DMA FIFO (DFIFO)       18–33         18.29       Interrupt Status (ISTAT)       18–34         18.30       Chip Test Eight (CTEST8)       18–37         18.31       Longitudinal Parity (LCRC)       18–36         18.32       DMA Byte Counter (DBC)       18–36         18.33       DMA Command (DCMD)       18–36         18.34       DMA Next Data Address (DNAD)       18–40         18.35       DMA Scripts Pointer (DSP)       18–40         18.36       DMA Scripts Pointer Save (DSPS)       18–41         18.39       DMA Interrupt Enable (DIEN)       18–42         18.40       DMA Watchdog Timer (DWT)       18–42         18.41       DMA Control Register (DCNTL)       18–42         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                 |

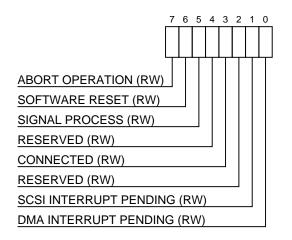

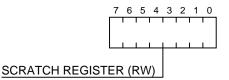

| 18.29       Interrupt Status (ISTAT)       18–34         18.30       Chip Test Eight (CTEST8)       18–37         18.31       Longitudinal Parity (LCRC)       18–38         18.32       DMA Byte Counter (DBC)       18–38         18.33       DMA Command (DCMD)       18–39         18.34       DMA Next Data Address (DNAD)       18–40         18.35       DMA Scripts Pointer (DSP)       18–40         18.36       DMA Scripts Pointer Save (DSPS)       18–41         18.37       Scratch Register (SCRATCH)       18–42         18.39       DMA Interrupt Enable (DIEN)       18–42         18.41       DMA Control Register (DCNTL)       18–42         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                |

| 18.31       Longitudinal Parity (LCRC)       18–38         18.32       DMA Byte Counter (DBC)       18–39         18.33       DMA Command (DCMD)       18–39         18.34       DMA Next Data Address (DNAD)       18–40         18.35       DMA Scripts Pointer (DSP)       18–40         18.36       DMA Scripts Pointer Save (DSPS)       18–40         18.37       Scratch Register (SCRATCH)       18–42         18.39       DMA Interrupt Enable (DIEN)       18–42         18.40       DMA Watchdog Timer (DWT)       18–42         18.41       DMA Control Register (DCNTL)       18–42         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                         |

| 18.31       Longitudinal Parity (LCRC)       18–38         18.32       DMA Byte Counter (DBC)       18–39         18.33       DMA Command (DCMD)       18–39         18.34       DMA Next Data Address (DNAD)       18–40         18.35       DMA Scripts Pointer (DSP)       18–40         18.36       DMA Scripts Pointer Save (DSPS)       18–40         18.37       Scratch Register (SCRATCH)       18–42         18.39       DMA Interrupt Enable (DIEN)       18–42         18.40       DMA Watchdog Timer (DWT)       18–42         18.41       DMA Control Register (DCNTL)       18–42         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                         |

| 18.33       DMA Command (DCMD)       18–39         18.34       DMA Next Data Address (DNAD)       18–40         18.35       DMA Scripts Pointer (DSP)       18–40         18.36       DMA Scripts Pointer Save (DSPS)       18–41         18.37       Scratch Register (SCRATCH)       18–42         18.39       DMA Interrupt Enable (DIEN)       18–42         18.40       DMA Watchdog Timer (DWT)       18–42         18.41       DMA Control Register (DCNTL)       18–42         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 18.34       DMA Next Data Address (DNAD)       18–40         18.35       DMA Scripts Pointer (DSP)       18–40         18.36       DMA Scripts Pointer Save (DSPS)       18–41         18.37       Scratch Register (SCRATCH)       18–42         18.38       DMA Mode (DMODE)       18–42         18.39       DMA Interrupt Enable (DIEN)       18–42         18.40       DMA Watchdog Timer (DWT)       18–42         18.41       DMA Control Register (DCNTL)       18–42         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

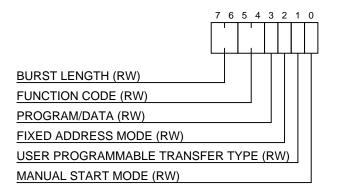

| 18.35       DMA Scripts Pointer (DSP)       18–40         18.36       DMA Scripts Pointer Save (DSPS)       18–41         18.37       Scratch Register (SCRATCH)       18–41         18.38       DMA Mode (DMODE)       18–42         18.39       DMA Interrupt Enable (DIEN)       18–42         18.40       DMA Watchdog Timer (DWT)       18–42         18.41       DMA Control Register (DCNTL)       18–42         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

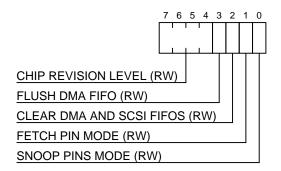

| 18.36       DMA Scripts Pointer Save (DSPS)       18–44         18.37       Scratch Register (SCRATCH)       18–44         18.38       DMA Mode (DMODE)       18–42         18.39       DMA Interrupt Enable (DIEN)       18–42         18.40       DMA Watchdog Timer (DWT)       18–44         18.41       DMA Control Register (DCNTL)       18–45         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18.37       Scratch Register (SCRATCH)       18–44         18.38       DMA Mode (DMODE)       18–42         18.39       DMA Interrupt Enable (DIEN)       18–43         18.40       DMA Watchdog Timer (DWT)       18–44         18.41       DMA Control Register (DCNTL)       18–45         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18.38       DMA Mode (DMODE)       18–42         18.39       DMA Interrupt Enable (DIEN)       18–43         18.40       DMA Watchdog Timer (DWT)       18–44         18.41       DMA Control Register (DCNTL)       18–45         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18.39       DMA Interrupt Enable (DIEN)       18–43         18.40       DMA Watchdog Timer (DWT)       18–44         18.41       DMA Control Register (DCNTL)       18–45         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 18.40       DMA Watchdog Timer (DWT)       18–44         18.41       DMA Control Register (DCNTL)       18–45         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

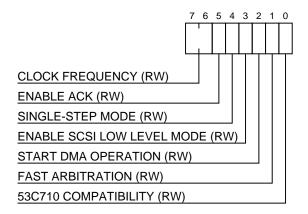

| 18.41       DMA Control Register (DCNTL)       18–45         18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18.42       Adder Sum Output (ADDER)       18–47         18.42.1       SCSI Script RAM Buffer       18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18.42.1         SCSI Script RAM Buffer         18–47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 18.42.2 Ethernet Station Address ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 18.42.3Serial Control Bus Interface18–48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18.42.4         FEPROM         18-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## Part IV The System Bus

# 19 The DEC 4000 System Bus

| 19.1     | Supported Transactions                        | 19–1  |

|----------|-----------------------------------------------|-------|

|          | Address Space                                 | 19–1  |

| 19.3     | System Bus Transactions                       | 19–2  |

| 19.3.1   | Bus Arbiter                                   | 19–2  |

| 19.3.2   | Transaction Process                           | 19–2  |

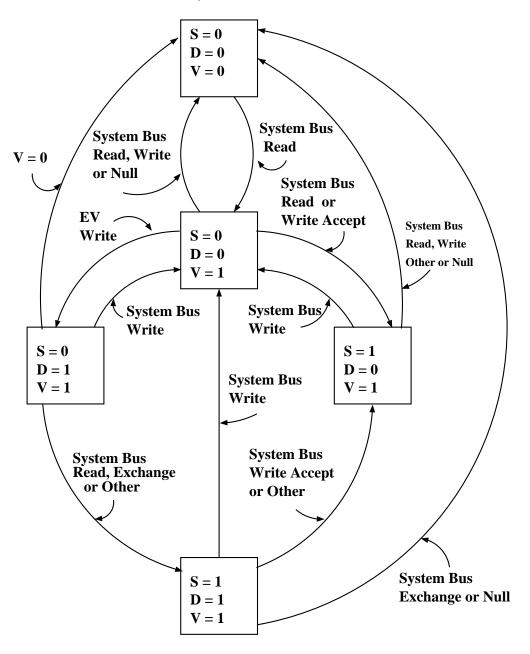

| 19.4     | Cache Protocol                                | 19–3  |

| 19.5     | System Bus Signals                            | 19–6  |

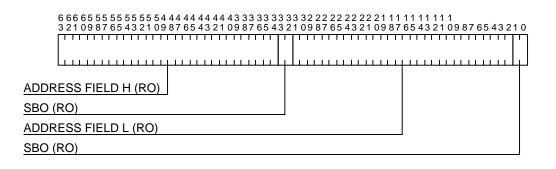

| 19.5.1   | Command and Address Format                    | 19–9  |

| 19.5.2   | Arbitration Signals                           | 19–9  |

| 19.5.3   | Protocol Signals                              | 19–10 |

| 19.5.4   | Address Field                                 | 19–11 |

| 19.5.5   | Response and Interrupt Signals                | 19–14 |

| 19.5.6   | Clocking and Initialization Signals           | 19–18 |

| 19.5.6.1 |                                               | 19–18 |

| 19.5.7   | Initialization Signals                        | 19–18 |

| 19.6     | System Bus Transactions and Timing            | 19–19 |

| 19.6.1   | Read and Read Exclusive Transactions          | 19–20 |

| 19.6.2   | Null Transactions                             | 19–24 |

| 19.6.3   | Memory Exchange Transactions                  | 19–26 |

| 19.6.4   | Memory Write Transactions                     | 19–28 |

| 19.6.5   | Noncacheable Address Space Write Transactions | 19–30 |

#### Part V The Firmware

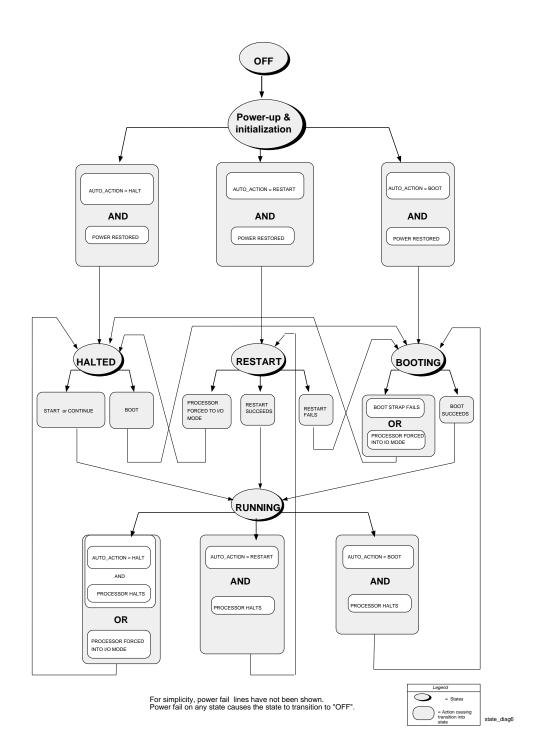

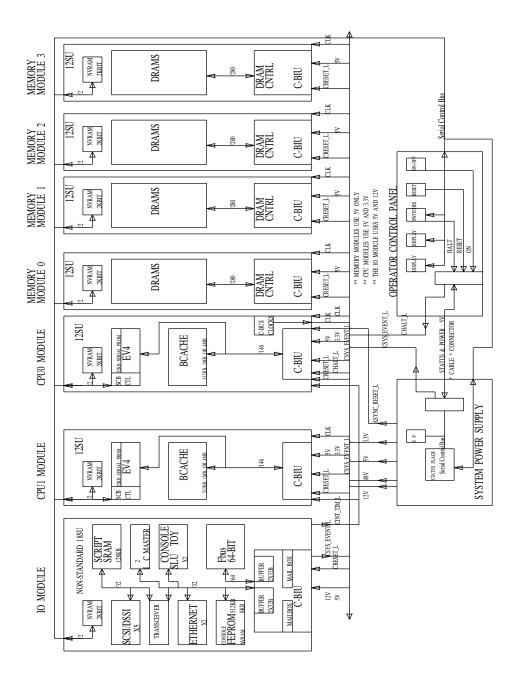

## 20 System State Transitions

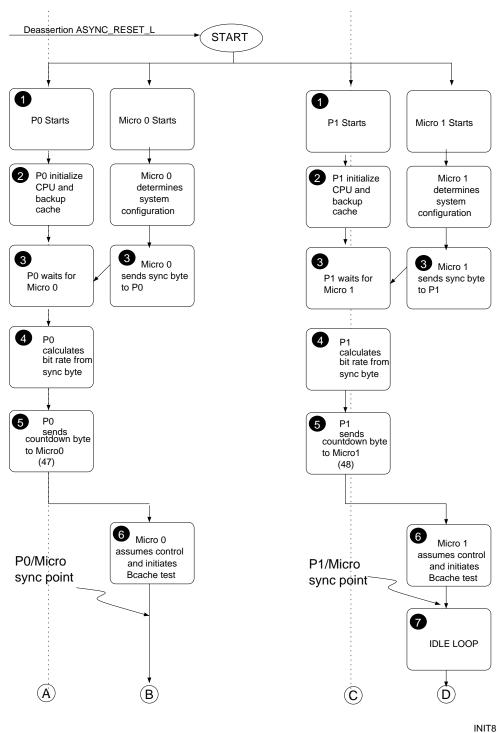

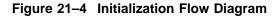

#### 21 The Power-Up and Initialization State

| 21.1     | The Powered Off State         | 21–2  |

|----------|-------------------------------|-------|

| 21.2     | The Power-up Process          | 21–2  |

| 21.2.1   | AC Power-Up                   | 21–4  |

| 21.2.2   | DC Power-Up                   | 21–4  |

| 21.2.3   | ASYNC_RESET_L and CRESET_L    | 21–5  |

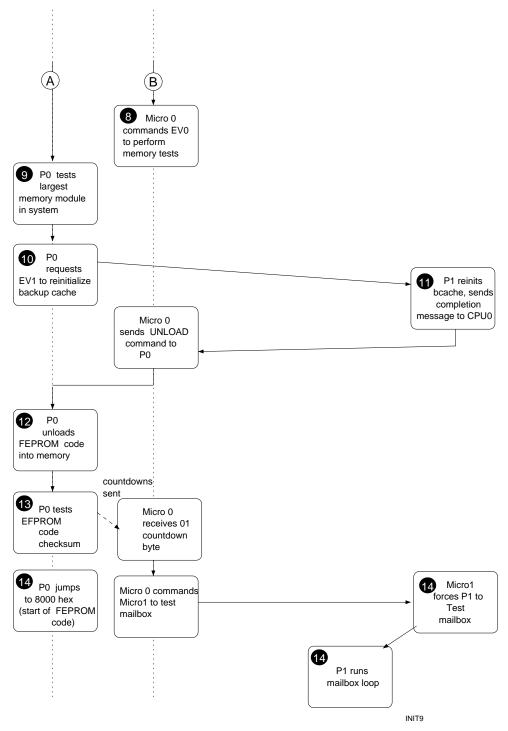

| 21.3     | System Initialization         | 21–6  |

| 21.3.1   | FEPROM Unloading              | 21–10 |

| 21.3.2   | Console Initialization        | 21–12 |

| 21.3.3   | Memory Testing                | 21–13 |

| 21.3.3.1 | Memory Testing and the Bitmap | 21–15 |

| 21.3.4   | Driver Initialization         | 21–15 |

| 21.3.4.1 | I I/O Adapter Configuration   | 21–17 |

#### 22 The Halted State

| 22.1 | The HALT command           | 22–2 |

|------|----------------------------|------|

| 22.2 | The HALT Switch on the OCP | 22–2 |

| 22.3 | System Error               | 22–2 |

#### 23 The Bootstrap State

| 23.2Environment Variables23–223.3Hardware Restart Parameter Block23–323.4Console Callback Routines23–323.5Boot Block Calling Interface23–423.6Boot Devices23–523.7Boot Parameters23–523.8Disk and Tape Booting23–623.9Ethernet Booting23–623.9.1MOP Booting23–723.9.2BOOTP booting23–723.9.2.1Setting up the Console for BOOTP Boots23–823.9.2.2Using BOOTP bootstrap23–10         | 23.1     | DEC 4000 Bootstrap Algorithm     | 23–2  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------|-------|

| 23.4Console Callback Routines23–323.5Boot Block Calling Interface23–423.6Boot Devices23–523.7Boot Parameters23–523.8Disk and Tape Booting23–623.9Ethernet Booting23–623.9.1MOP Booting23–723.9.2BOOTP booting23–723.9.2Setting up the Console for BOOTP Boots23–823.9.2Setting up the Console for BOOTP Boots23–8                                                                  | 23.2     | Environment Variables            | 23–2  |

| 23.5Boot Block Calling Interface23–423.6Boot Devices23–523.7Boot Parameters23–523.8Disk and Tape Booting23–623.9Ethernet Booting23–623.9.1MOP Booting23–723.9.2BOOTP booting23–723.9.2Setting up the Console for BOOTP Boots23–823.923–8                                                                                                                                           | 23.3     | Hardware Restart Parameter Block | 23–3  |

| 23.6       Boot Devices       23–5         23.7       Boot Parameters       23–5         23.8       Disk and Tape Booting       23–6         23.9       Ethernet Booting       23–6         23.9.1       MOP Booting       23–7         23.9.2       BOOTP booting       23–7         23.9.2.1       Setting up the Console for BOOTP Boots       23–8                             | 23.4     | Console Callback Routines        | 23–3  |

| 23.6       Boot Devices       23–5         23.7       Boot Parameters       23–5         23.8       Disk and Tape Booting       23–6         23.9       Ethernet Booting       23–6         23.9.1       MOP Booting       23–7         23.9.2       BOOTP booting       23–7         23.9.2.1       Setting up the Console for BOOTP Boots       23–8                             | 23.5     | Boot Block Calling Interface     | 23–4  |

| 23.8       Disk and Tape Booting       23–6         23.9       Ethernet Booting       23–6         23.9.1       MOP Booting       23–7         23.9.2       BOOTP booting       23–7         23.9.2       BOOTP booting       23–7         23.9.2       Setting up the Console for BOOTP Boots       23–8         23.9.2.1       Setting up the Console for BOOTP Boots       23–8 | 23.6     |                                  | 23–5  |

| 23.9       Ethernet Booting       23–6         23.9.1       MOP Booting       23–7         23.9.1       MOP Network "Listening"       23–7         23.9.2       BOOTP booting       23–8         23.9.2.1       Setting up the Console for BOOTP Boots       23–8                                                                                                                  | 23.7     | Boot Parameters                  | 23–5  |

| 23.9.1         MOP Booting         23–7           23.9.1.1         MOP Network "Listening"         23–7           23.9.2         BOOTP booting         23–8           23.9.2.1         Setting up the Console for BOOTP Boots         23–8                                                                                                                                         | 23.8     | Disk and Tape Booting            | 23–6  |

| 23.9.1.1MOP Network "Listening"23–723.9.2BOOTP booting23–823.9.2.1Setting up the Console for BOOTP Boots23–8                                                                                                                                                                                                                                                                       | 23.9     | Ethernet Booting                 | 23–6  |

| 23.9.2BOOTP booting23-823.9.2.1Setting up the Console for BOOTP Boots23-8                                                                                                                                                                                                                                                                                                          | 23.9.1   | MOP Booting                      | 23–7  |

| 23.9.2.1 Setting up the Console for BOOTP Boots                                                                                                                                                                                                                                                                                                                                    | 23.9.1.  | 1 MOP Network "Listening"        | 23–7  |

|                                                                                                                                                                                                                                                                                                                                                                                    | 23.9.2   | BOOTP booting                    | 23–8  |

| 23.9.2.2 Using BOOTP bootstrap 23–10                                                                                                                                                                                                                                                                                                                                               | 23.9.2.1 |                                  | 23–8  |

|                                                                                                                                                                                                                                                                                                                                                                                    | 23.9.2.2 | 2 Using BOOTP bootstrap          | 23–10 |

### 24 The Restart State

| 24.1 | Restart Failure    | 24–2 |

|------|--------------------|------|

| 24.2 | Restart Parameters | 24–3 |

#### 25 Console

| 25.1   | Console Prompt                            | 25–1  |

|--------|-------------------------------------------|-------|

| 25.2   | Command Conventions                       | 25–1  |

| 25.3   | Console Special Characters                | 25–2  |

| 25.4   | Environment Variables                     | 25–3  |

| 25.5   | Command Overview                          | 25–3  |

| 25.6   | Getting Information About the System      | 25–4  |

| 25.7   | Online HELP                               | 25–5  |

| 25.8   | Examining and Depositing                  | 25–7  |

| 25.8.1 | Accessing Memory                          | 25–8  |

| 25.8.2 | Examining registers                       | 25–9  |

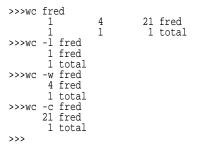

| 25.9   | Using Pipes ( ) and grep to Filter Output | 25–10 |

| 25.10  | Using I/O Redirection (>)                 | 25–11 |

| 25.11  | Running Commands in the Background "&"    | 25–11 |

| 25.12  | Monitoring Status                         | 25–12 |

| 25.13  | Killing a Process                         | 25–13 |

| 25.14  | Creating Scripts                          | 25–13 |

| 25.15  | Using Flow Control                        | 25–14 |

| 25.16  | Console Shell                             | 25–16 |

|        |                                           |       |

## 26 Diagnostics

| 26.1 Di    | agnostic Overview                                        | 26–1  |

|------------|----------------------------------------------------------|-------|

| 26.1.1     | Diagnostic Classes                                       | 26–1  |

| 26.1.2     | Diagnostic User Interface                                | 26–2  |

| 26.1.2.1   | Starting Diagnostic Tests and Exercisers                 | 26–2  |

| 26.1.2.2   | Diagnostic Control Flags                                 | 26–2  |

| 26.1.2.2.1 | Global Diagnostic Environment Variables                  | 26–3  |

| 26.1.2.2.2 | Local Diagnostic Command Qualifiers for most diagnostics | 26–3  |

| 26.1.2.2.3 | Local Diagnostic Command Qualifiers for specific         |       |

|            | diagnostics                                              | 26–3  |

| 26.1.2.3   | Monitoring the Exerciser Status                          | 26–3  |

| 26.1.2.4   | Terminating Diagnostic Tests and Exercisers              | 26–4  |

| 26.1.3     | Diagnostic Output Displays                               | 26–4  |

| 26.1.3.1   | Operator Control Panel LED Displays                      | 26–4  |

| 26.1.3.2   | Console Terminal Error Messages                          | 26–5  |

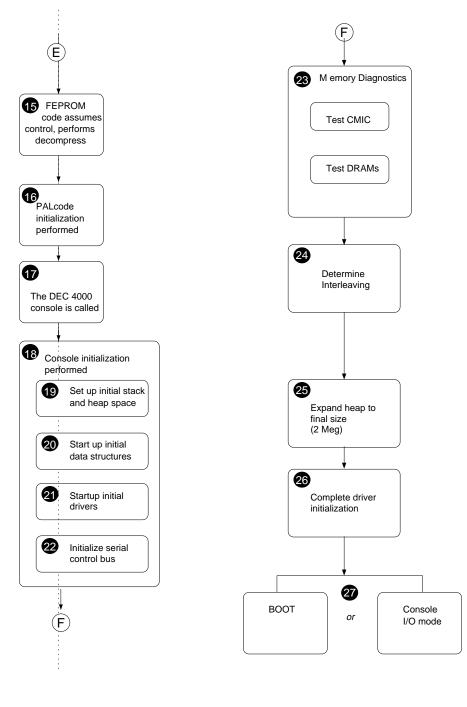

| 26.1.4     | Startup Message                                          | 26–6  |

| 26.1.5     | Completion Message                                       | 26–7  |

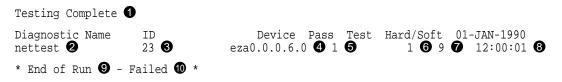

| 26.1.6     | End-of-pass Message                                      | 26–7  |

| 26.1.7     | Test Trace Message                                       | 26–8  |

| 26.1.8     | Diagnostic Power-up Flow                                 | 26–8  |

| 26.2 CI    | PU/Cache Subsystem                                       | 26–9  |

| 26.2.1     | Diagnostic Strategy                                      | 26–9  |

| 26.2.2     | Power-up Strategy                                        | 26–9  |

| 26.2.3     | Fault Architecture                                       | 26–9  |

| 26.2.4     | Interpreting Error Printouts                             | 26–9  |

| 26.2.5     | Error Message Display                                    | 26–9  |

| 26.2.6     | Test name: B-Cache init                                  | 26–10 |

| 26.2.7     | Test name: SROM Address Test                             | 26–10 |

| 26.2.8     | Test name: SROM Tag Store Test                           | 26–11 |

| 26.2.9     | Test name: SROM B-Cache Data Line Test                   | 26–12 |

| 26.2.10    | Test name: SROM ECC test                                 | 26–13 |

| 26.2.11    | Test name: CPU Spin on Processor Mailbox                 | 26–14 |

| 26.2.12    | Test name: Cbus (System Bus) test                        | 26–14 |

|            |                                                          |       |

| 26.2.13   | Test name: Disable failing CPU          | 26–15 |

|-----------|-----------------------------------------|-------|

| 26.2.14   | Test name: Memory test                  | 26–15 |

| 26.2.15   | Test name: Unload                       | 26–16 |

| 26.3 Me   | emory Subsystem                         | 26–19 |

| 26.3.1    | Initialization                          | 26–19 |

| 26.3.1.1  | Initialization Tests                    | 26–19 |

| 26.3.1.2  | Memory Configuration                    | 26–20 |

| 26.3.1.3  | Failure Reporting and Logging           | 26–21 |

| 26.3.2    | Exerciser Tests                         | 26–21 |

| 26.4 SC   | SI/DSSI Subsystem                       | 26–21 |

| 26.4.1    | Expected Failures                       | 26–22 |

| 26.4.2    | Diagnostic Strategy                     | 26–22 |

| 26.4.3    | Power-up Tests                          | 26–22 |

| 26.4.3.1  | IO Module Self Tests                    | 26–23 |

| 26.4.3.2  | Driver Startup/Sizing                   | 26–23 |

| 26.4.3.3  | Disk/Tape Unit Self Tests               | 26–23 |

| 26.4.4    | Functional Tests                        | 26–23 |

| 26.4.5    | Exerciser Tests                         | 26–24 |

| 26.5 Ne   | twork Subsystem                         | 26–24 |

| 26.5.1    | Initialization                          | 26–24 |

| 26.5.1.1  | Driver Initialization Tests             | 26–24 |

| 26.5.2    | Exerciser Tests                         | 26–25 |

| 26.6 Fu   | turebus+ Subsystem                      | 26–25 |

| 26.6.0.1  | Hardware Overview                       | 26–25 |

| 26.7 Fu   | turebus+ Devices                        | 26–26 |

| 26.7.1    | Hardware Overview                       | 26–26 |

| 26.7.1.1  | Diagnostic Strategy                     | 26–26 |

| 26.7.2    | Futurebus+ Sizing                       | 26–26 |

| 26.8 SL   | U Subsystem                             | 26–27 |

| 26.8.1    | Overview                                | 26–27 |

| 26.8.1.1  | Hardware Overview                       | 26–27 |

| 26.8.2    | 85C30 Register Test                     | 26–27 |

| 26.8.3    | 85C30 Internal Loop-back Test           | 26–28 |

| 26.8.4    | 85C30 External Loop-back Test           | 26–28 |

|           | ılti-Processor                          | 26–28 |

| 26.10 Set | rial Control Bus Subsystem              | 26–29 |

| 26.10.1   | Controller Register Test (iic_reg_test) | 26–29 |

| 26.10.2   | Bus Access Test (iic_acc_test)          | 26–29 |

## A IPR State on Power-up and RESET

| A.1   | TB Miss Flows | A–2 |

|-------|---------------|-----|

| A.1.1 | ITB Miss      | A–3 |

| A.1.2 | DTB Miss      | A–3 |

#### **B** Error Flows

| I-stream ECC error                                         | B–1                                                                                                                                                                   |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D-stream ECC error                                         | B–1                                                                                                                                                                   |

| BIU: tag address parity error                              | B–2                                                                                                                                                                   |

|                                                            | B–2                                                                                                                                                                   |

| BIU: system external transaction terminated with CACK_SERR | B–2                                                                                                                                                                   |

| BIU: system transaction terminated with CACK_HERR          | B–2                                                                                                                                                                   |

| BIU: I-stream parity error (parity mode only)              | B–2                                                                                                                                                                   |