# Personal Computer Service Manual

PC-8201

**NEC** NEC Corporation

¢1 PTS-238

© 1983 NEC Corporation Tokyo, Japan

1

ξ.

**≺**

All rights reserved. No part of this publication may be reproduced in whole or in part without the prior written permission of NEC Corporation.

# CONTENTS

•

| CHAPTER 1       INTRODUCTION         1.1       Specifications       1-1         1.2       Switches and Contrast VR       1-3         CHAPTER 2       EXTERNAL VIEW       1-3         CHAPTER 3       FUNCTIONAL SPECIFICATIONS       3-1         3.1       Logical Specifications       3-1         3.1.1       CPU       3-1         3.1.2       ROM       3-1         3.1.3       RAM       3-1         3.1.4       LCD Interface       3-3         3.1.5       Printer Interface       3-3         3.1.6       Calendar Clock Interface       3-4         3.1.7       Keyboard Interface       3-1         3.1.8       Serial Interface       3-10         3.1.9       Cassette Interface       3-13         3.1.10       Bar Code Reader Interface       3-13         3.1.11       Interrupt Functions       3-14         3.1.12       I/O Address       3-21         3.2.1       Signal Lines       3-21         3.2.1       Signal Lines       3-21         3.2.2       Physical Specifications       3-21         3.2.3       Structure and Size       3-30         3.3       In                                                                                                                                                                                                                   |         |        | ۲                                                                                                                                  | Ļ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------|---|

| 1.2       Switches and Contrast VR       1–3         CHAPTER 2 EXTERNAL VIEW         CHAPTER 3 FUNCTIONAL SPECIFICATIONS         3.1       Logical Specifications       3–1         3.1.1       CPU       3–1         3.1.2       ROM       3–1         3.1.3       RAM       3–1         3.1.4       LCD Interface       3–1         3.1.5       Printer Interface       3–3         3.1.6       Calendar Clock Interface       3–8         3.1.7       Keyboard Interface       3–10         3.1.8       Serial Interface       3–13         3.1.10       Bar Code Reader Interface       3–13         3.1.11       Interrupt Functions       3–14         3.1.12       I/O Address       3–21         3.2.1       Signal Lines       3–21         3.2.2       Power Supply       3–29         3.2.3       Structure and Size       3–30         3.4       Software Interface       3–30         3.5       Human Interface       3–30         3.6       Performance Specification for the PC-8201       3–33         3.7       Accessories       3–33         3.7       Accessories                                                                                                                                                                                                                     | CHAPTER |        |                                                                                                                                    |   |

| CHAPTER 2 EXTERNAL VIEW         CHAPTER 3 FUNCTIONAL SPECIFICATIONS         3.1       Logical Specifications       3-1         3.1.1       CPU       3-1         3.1.2       ROM       3-1         3.1.3       RAM       3-1         3.1.4       LCD Interface       3-3         3.1.5       Printer Interface       3-3         3.1.6       Calendar Clock Interface       3-7         3.1.6       Calendar Clock Interface       3-8         3.1.7       Keyboard Interface       3-10         3.1.9       Casette Interface       3-13         3.1.10       Bar Code Reader Interface       3-13         3.1.11       Interrupt Functions       3-14         3.1.12       I/O Address       3-21         3.2.1       Signal Lines       3-21         3.2.2       Power Supply       3-29         3.2.3       Structure and Size       3-30         3.4       Software Interface       3-30         3.5       Human Interface       3-30         3.6       Performance Specification for the PC-8201       3-33         3.7       Accessories       3-33         3.7       Accessories       3-34                                                                                                                                                                                                       |         | 1.1    | Specifications $\dots \dots \dots$ |   |

| CHAPTER 3 FUNCTIONAL SPECIFICATIONS         3.1       Logical Specifications       3-1         3.1.1       CPU       3-1         3.1.2       ROM       3-1         3.1.3       RAM       3-1         3.1.4       LCD Interface       3-3         3.1.5       Printer Interface       3-7         3.1.6       Calendar Clock Interface       3-8         3.1.7       Keyboard Interface       3-10         3.1.8       Serial Interface       3-13         3.1.10       Bar Code Reader Interface       3-13         3.1.11       Interrupt Functions       3-14         3.1.12       I/O Address       3-13         3.1.11       Interrupt Functions       3-14         3.1.12       I/O Address       3-21         3.2.2       Power Supply       3-21         3.2.3       Structure and Size       3-30         3.4       Software Interface       3-30         3.5       Human Interface       3-30         3.6       Performance Specification for the PC-8201       3-33         3.7       Accessories       3-33         3.7       Accessories       3-33         3.7       Accessories <td></td> <td>1.2</td> <td>Switches and Contrast VR <math>\ldots</math> <math>\ldots</math> <math>\ldots</math> <math>\ldots</math> <math>\ldots</math> <math>\ldots</math> <math>1-3</math></td> <td></td> |         | 1.2    | Switches and Contrast VR $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1-3$                                               |   |

| 3.1       Logical Specifications       3-1         3.1.1       CPU       3-1         3.1.2       ROM       3-1         3.1.3       RAM       3-1         3.1.4       LCD Interface       3-3         3.1.5       Printer Interface       3-7         3.1.6       Calendar Clock Interface       3-8         3.1.7       Keyboard Interface       3-9         3.1.8       Serial Interface       3-10         3.1.9       Cassette Interface       3-13         3.1.10       Bar Code Reader Interface       3-13         3.1.11       Interrupt Functions       3-14         3.1.12       I/O Address       3-21         3.2.1       Signal Lines       3-21         3.2.2       Power Supply       3-23         3.2.3       Structure and Size       3-30         3.4       Software Interface       3-30         3.5       Human Interface       3-330         3.6       Performance Specification for the PC-8201       3-33         3.7       Accessories       3-33         3.7       Accessories       3-33         3.7       Accessories       3-33         3.7       A                                                                                                                                                                                                                            | CHAPTER | 2 EX   | TERNAL VIEW                                                                                                                        |   |

| 3.1       Logical Specifications       3-1         3.1.1       CPU       3-1         3.1.2       ROM       3-1         3.1.3       RAM       3-1         3.1.4       LCD Interface       3-3         3.1.5       Printer Interface       3-7         3.1.6       Calendar Clock Interface       3-8         3.1.7       Keyboard Interface       3-9         3.1.8       Serial Interface       3-10         3.1.9       Cassette Interface       3-13         3.1.10       Bar Code Reader Interface       3-13         3.1.11       Interrupt Functions       3-14         3.1.12       I/O Address       3-21         3.2.1       Signal Lines       3-21         3.2.2       Power Supply       3-23         3.2.3       Structure and Size       3-30         3.4       Software Interface       3-30         3.5       Human Interface       3-330         3.6       Performance Specification for the PC-8201       3-33         3.7       Accessories       3-33         3.7       Accessories       3-33         3.7       Accessories       3-33         3.7       A                                                                                                                                                                                                                            | CHAPTER | 3 FU   | NCTIONAL SPECIFICATIONS                                                                                                            |   |

| 3.1.1       CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | 3.1    | Logical Specifications                                                                                                             |   |

| 3.1.3       RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | 3.1.1  | CPU                                                                                                                                |   |

| 3.1.4       LCD Interface       3-3         3.1.5       Printer Interface       3-7         3.1.6       Calendar Clock Interface       3-7         3.1.6       Calendar Clock Interface       3-7         3.1.7       Keyboard Interface       3-9         3.1.8       Serial Interface       3-10         3.1.9       Cassette Interface       3-13         3.1.10       Bar Code Reader Interface       3-13         3.1.11       Interrupt Functions       3-14         3.1.12       I/O Address       3-15         3.2       Physical Specifications       3-21         3.2.1       Signal Lines       3-21         3.2.2       Power Supply       3-29         3.2.3       Structure and Size       3-30         3.4       Software Interface       3-30         3.5       Human Interface       3-30         3.6       Performance Specification for the PC-8201       3-33         3.7       Accessories       3-33         3.7       Accessories       3-33         3.7       Accessories       3-33         3.7       Accessories       4-1         4.1       Disassembly       4-1      <                                                                                                                                                                                                       |         | 3.1.2  | ROM                                                                                                                                |   |

| 3.1.5       Printer Interface       3-7         3.1.6       Calendar Clock Interface       3-8         3.1.7       Keyboard Interface       3-9         3.1.8       Serial Interface       3-10         3.1.9       Cassette Interface       3-13         3.1.10       Bar Code Reader Interface       3-13         3.1.11       Interrupt Functions       3-14         3.1.12       I/O Address       3-13         3.1.11       Interrupt Functions       3-14         3.1.12       J/O Address       3-13         3.2       Physical Specifications       3-21         3.2.1       Signal Lines       3-21         3.2.2       Power Supply       3-29         3.2.3       Structure and Size       3-30         3.4       Software Interface       3-30         3.5       Human Interface       3-30         3.6       Performance Specification for the PC-8201       3-33         3.7       Accessories       3-33         3.7       Accessories       3-33         3.7       Accessories       4-1         4.1.1       PC-8201 Cover       4-1         4.1.2       LCD Board       4-2      <                                                                                                                                                                                                       |         | 3.1.3  | RAM                                                                                                                                |   |

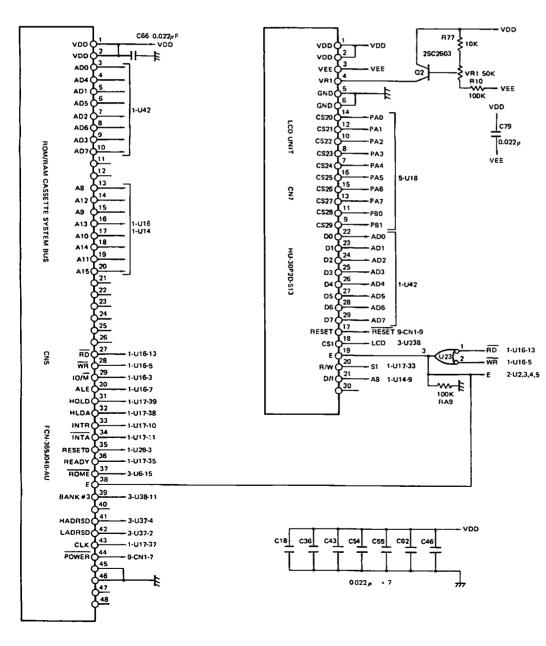

| 3.1.6       Calendar Clock Interface       3-8         3.1.7       Keyboard Interface       3-9         3.1.8       Serial Interface       3-10         3.1.9       Cassette Interface       3-13         3.1.10       Bar Code Reader Interface       3-13         3.1.11       Interrupt Functions       3-14         3.1.12       I/O Address       3-14         3.1.12       Byoscifications       3-21         3.2.2       Power Supply       3-29         3.2.3       Structure and Size       3-30         3.4       Software Interface       3-30         3.5       Human Interface       3-30         3.6       Performance Specification for the PC-8201       3-33         3.7       Accessories       3-33         3.7       Accessories       3-33         3.7       Accessories       3-33         3.7       Accessories       4-1         4.1.1       PC-8201 Cover       4-1         4.1.2       LCD Board       4-2         4.1.3       Keyboard       4-2         4.1.4       Power Supply Board       4-3         4.2.1       LCD Board       4-3         4.2.2                                                                                                                                                                                                                        |         | 3.1.4  | LCD Interface $$                                                                                                                   |   |

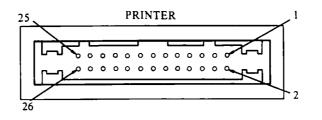

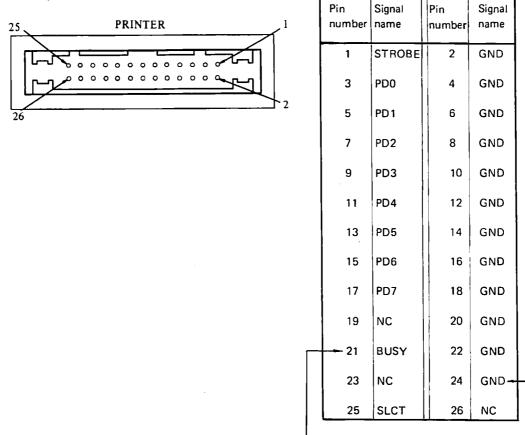

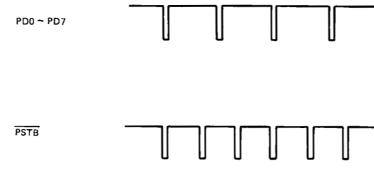

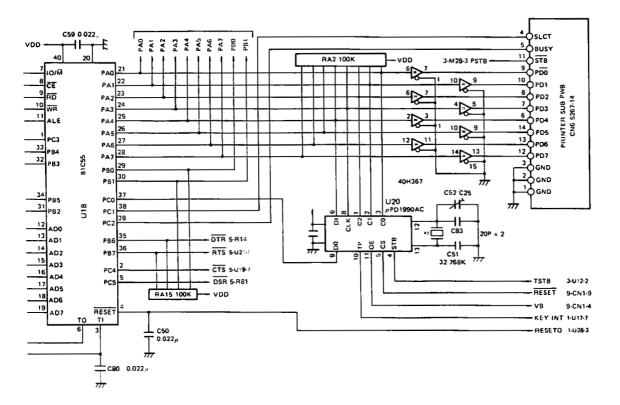

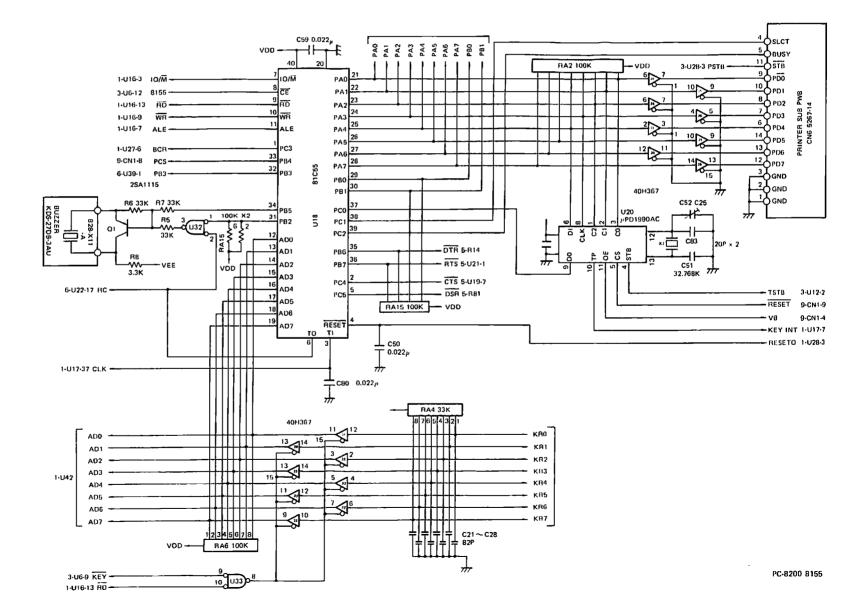

| 3.1.7       Keyboard Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | 3.1.5  | Printer Interface                                                                                                                  |   |

| 3.1.8       Serial Interface       .3-10         3.1.9       Cassette Interface       .3-13         3.1.10       Bar Code Reader Interface       .3-13         3.1.11       Interrupt Functions       .3-14         3.1.12       I/O Address       .3-15         3.2       Physical Specifications       .3-21         3.2.1       Signal Lines       .3-21         3.2.2       Power Supply       .3-29         3.3       Interface to Other Hardware       .3-30         3.4       Software Interface       .3-30         3.5       Human Interface       .3-30         3.6       Performance Specification for the PC-8201       .3-33         3.7       Accessories       .3-33         CHAPTER 4       DISASSEMBLY/REASSEMBLY       4-1         4.1.1       PC-8201 Cover       .4-1         4.1.2       LCD Board       .4-2         4.1.3       Keyboard       .4-3         4.2       Reassembly       .4-3         4.2       Reassembly       .4-3         4.2.1       LCD Board       .4-3         4.2.2       Keyboard       .4-3         4.2.3       Keyboard       .4-3                                                                                                                                                                                                                       |         | 3.1.6  | Calendar Clock Interface                                                                                                           |   |

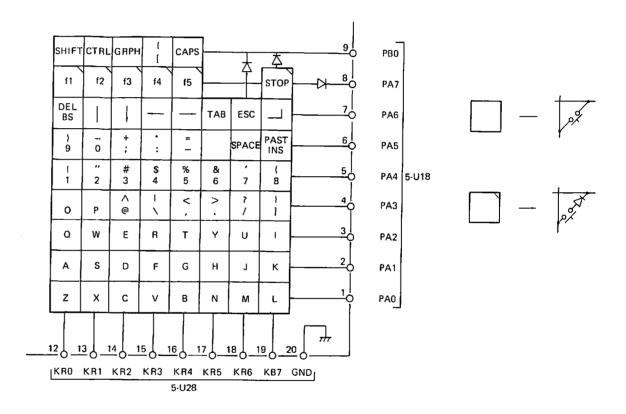

| 3.1.9       Cassette Interface       .3-13         3.1.10       Bar Code Reader Interface       .3-13         3.1.11       Interrupt Functions       .3-14         3.1.12       I/O Address       .3-15         3.2       Physical Specifications       .3-21         3.2.1       Signal Lines       .3-21         3.2.2       Power Supply       .3-29         3.2.3       Structure and Size       .3-30         3.4       Software Interface       .3-30         3.5       Human Interface       .3-30         3.6       Performance Specification for the PC-8201       .3-33         3.7       Accessories       .3-33         3.7       Accessories       .3-33         3.7       Accessories       .4-1         4.1.1       PC-8201 Cover       .4-1         4.1.2       LCD Board       .4-2         4.1.3       Keyboard       .4-2         4.1.4       Power Supply Board       .4-3         4.2       Reassembly       .4-3         4.2.1       LCD Board       .4-3         4.2.2       Keyboard       .4-3         4.2.3       Keyboard       .4-3         4.2.4                                                                                                                                                                                                                             |         | 3.1.7  | Keyboard Interface                                                                                                                 |   |

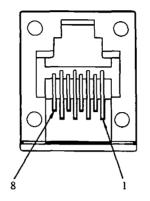

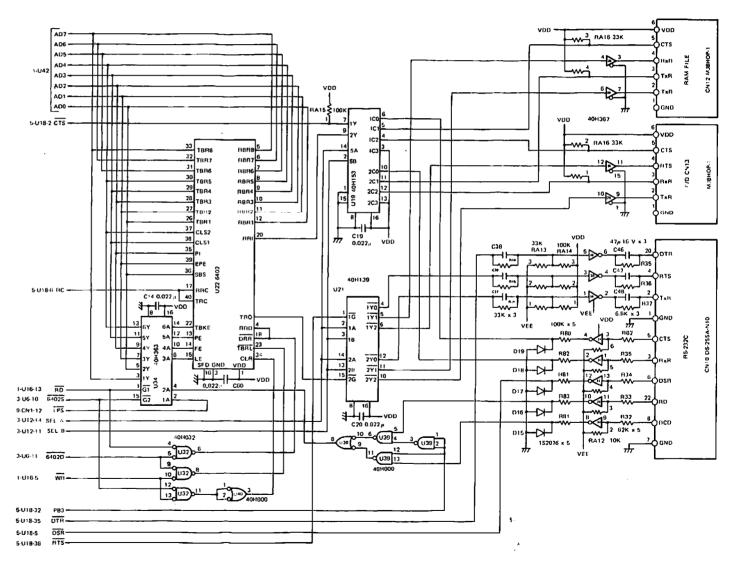

| 3.1.10 Bar Code Reader Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | 3.1.8  | Serial Interface                                                                                                                   |   |

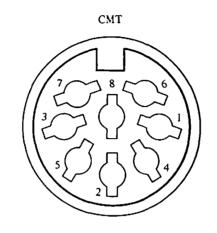

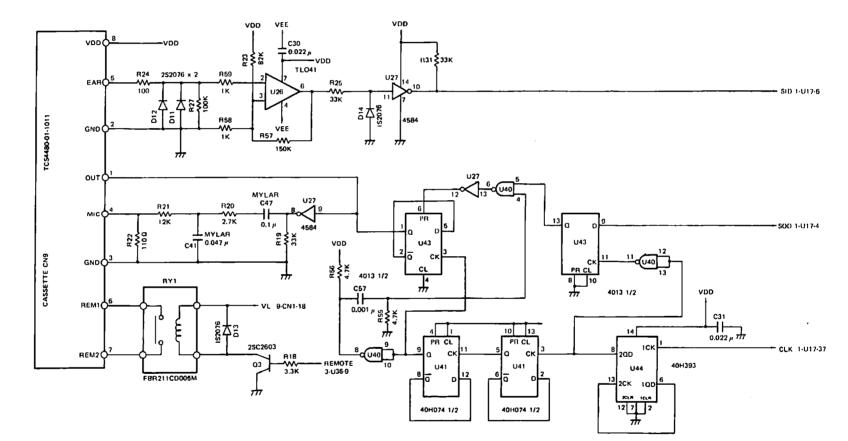

| 3.1.11       Interrupt Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | 3.1.9  | Cassette Interface                                                                                                                 |   |

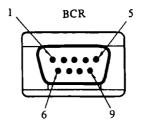

| 3.1.12       I/O Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | 3.1.10 | Bar Code Reader Interface                                                                                                          |   |

| 3.2       Physical Specifications       .3-21         3.2.1       Signal Lines       .3-21         3.2.2       Power Supply       .3-29         3.2.3       Structure and Size       .3-30         3.3       Interface to Other Hardware       .3-30         3.4       Software Interface       .3-30         3.5       Human Interface       .3-30         3.6       Performance Specification for the PC-8201       .3-33         3.7       Accessories       .3-33         3.7       Accessories       .3-33         CHAPTER 4       DISASSEMBLY/REASSEMBLY       .3-33         CHAPTER 4       DISASSEMBLY/REASSEMBLY       .4-1         4.1.1       PC-8201 Cover       .4-1         4.1.2       LCD Board       .4-2         4.1.3       Keyboard       .4-2         4.1.4       Power Supply Board       .4-3         4.2       Reassembly       .4-3         4.2.1       LCD Board       .4-3         4.2.2       Keyboard       .4-3         4.2.3       Keyboard       .4-3         4.2.4       Power Supply Board       .4-3                                                                                                                                                                                                                                                                   |         | 3.1.11 | Interrupt Functions $\ldots$                      |   |

| 3.2.1       Signal Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | 3.1.12 | 2 I/O Address                                                                                                                      |   |

| 3.2.2       Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | 3.2    | Physical Specifications                                                                                                            |   |

| 3.2.3       Structure and Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | 3.2.1  |                                                                                                                                    |   |

| 3.3       Interface to Other Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | 3.2.2  | Power Supply                                                                                                                       |   |

| 3.4       Software Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | 3.2.3  | Structure and Size                                                                                                                 |   |

| 3.5       Human Interface       3-30         3.6       Performance Specification for the PC-8201       3-33         3.7       Accessories       3-33         CHAPTER 4       DISASSEMBLY/REASSEMBLY         4.1       Disassembly       4-1         4.1.1       PC-8201 Cover       4-1         4.1.2       LCD Board       4-2         4.1.3       Keyboard       4-2         4.1.4       Power Supply Board       4-2         4.1.5       Main Board       4-3         4.2       Reassembly       4-3         4.2.1       LCD Board       4-3         4.2.2       Reassembly       4-3         4.2.3       Keyboard       4-4         4.2.3       Keyboard       4-4         4.2.4       Power Supply Board       4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         | 3.3    | Interface to Other Hardware                                                                                                        |   |

| 3.6       Performance Specification for the PC-8201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | 3.4    | Software Interface                                                                                                                 |   |

| 3.7 Accessories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | 3.5    | Human Interface                                                                                                                    |   |

| CHAPTER 4 DISASSEMBLY/REASSEMBLY         4.1 Disassembly       4-1         4.1.1 PC-8201 Cover       4-1         4.1.2 LCD Board       4-2         4.1.3 Keyboard       4-2         4.1.4 Power Supply Board       4-2         4.1.5 Main Board       4-3         4.2 Reassembly       4-3         4.2.1 LCD Board       4-3         4.2.2 Keyboard       4-3         4.2.3 Keyboard Switch       4-4         4.2.4 Power Supply Board       4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | 3.6    | Performance Specification for the PC-8201                                                                                          |   |

| 4.1       Disassembly       4-1         4.1.1       PC-8201 Cover       4-1         4.1.2       LCD Board       4-2         4.1.3       Keyboard       4-2         4.1.4       Power Supply Board       4-2         4.1.5       Main Board       4-3         4.2       Reassembly       4-3         4.2.1       LCD Board       4-3         4.2       Reassembly       4-3         4.2.1       LCD Board       4-3         4.2.2       Keyboard       4-3         4.2.3       Keyboard       4-4         4.2.3       Keyboard       4-4         4.2.4       Power Supply Board       4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | 3.7    | Accessories                                                                                                                        |   |

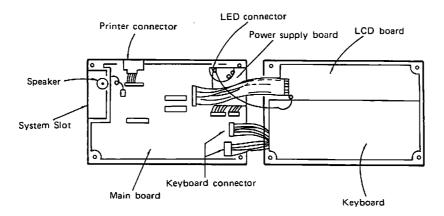

| 4.1       Disassembly       4-1         4.1.1       PC-8201 Cover       4-1         4.1.2       LCD Board       4-2         4.1.3       Keyboard       4-2         4.1.4       Power Supply Board       4-2         4.1.5       Main Board       4-3         4.2       Reassembly       4-3         4.2.1       LCD Board       4-3         4.2       Reassembly       4-3         4.2.1       LCD Board       4-3         4.2.2       Keyboard       4-3         4.2.3       Keyboard       4-4         4.2.3       Keyboard       4-4         4.2.4       Power Supply Board       4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CHAPTER | 24 DI  | SASSEMBLY/REASSEMBLY                                                                                                               |   |

| 4.1.1       PC-8201 Cover       4-1         4.1.2       LCD Board       4-2         4.1.3       Keyboard       4-2         4.1.4       Power Supply Board       4-2         4.1.5       Main Board       4-2         4.1.5       Main Board       4-3         4.2       Reassembly       4-3         4.2.1       LCD Board       4-3         4.2.2       Keyboard       4-3         4.2.3       Keyboard       4-4         4.2.4       Power Supply Board       4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0       |        |                                                                                                                                    |   |

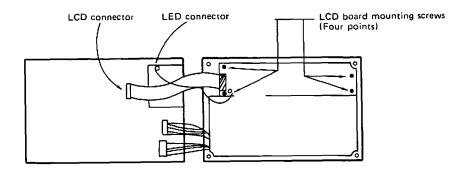

| 4.1.2       LCD Board       4-2         4.1.3       Keyboard       4-2         4.1.4       Power Supply Board       4-2         4.1.5       Main Board       4-3         4.2       Reassembly       4-3         4.2.1       LCD Board       4-3         4.2.2       Keyboard       4-3         4.2.3       Keyboard       4-4         4.2.4       Power Supply Board       4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |        |                                                                                                                                    |   |

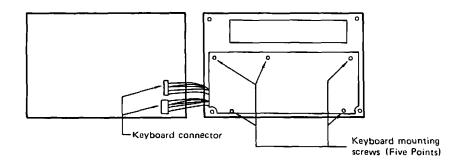

| 4.1.3       Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |        |                                                                                                                                    |   |

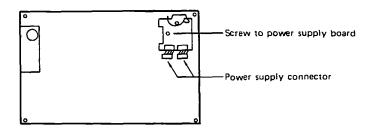

| 4.1.4       Power Supply Board       4.2         4.1.5       Main Board       4.3         4.2       Reassembly       4.3         4.2.1       LCD Board       4.3         4.2.2       Keyboard       4.4         4.2.3       Keyboard       4.4         4.2.4       Power Supply Board       4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |        |                                                                                                                                    |   |

| 4.1.5       Main Board       4.2       4.3         4.2       Reassembly       4.3         4.2.1       LCD Board       4.3         4.2.2       Keyboard       4.4         4.2.3       Keyboard       4.4         4.2.4       Power Supply Board       4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |        | Power Supply Board $4-2$                                                                                                           |   |

| 4.2       Reassembly       4-3         4.2.1       LCD Board       4-3         4.2.2       Keyboard       4-4         4.2.3       Keyboard Switch       4-4         4.2.4       Power Supply Board       4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |        |                                                                                                                                    |   |

| 4.2.1       LCD Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |        |                                                                                                                                    |   |

| 4.2.2       Keyboard       4.4         4.2.3       Keyboard Switch       4.4         4.2.4       Power Supply Board       4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |        |                                                                                                                                    |   |

| 4.2.3       Keyboard Switch       4-4         4.2.4       Power Supply Board       4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |        |                                                                                                                                    |   |

| 4.2.4 Power Supply Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |        | Keyboard Switch $4-4$                                                                                                              |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |        |                                                                                                                                    |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |        |                                                                                                                                    |   |

-i-

(?

i A

|         | 2.6 ROM                                     | 5  |

|---------|---------------------------------------------|----|

|         | 3 Installation                              |    |

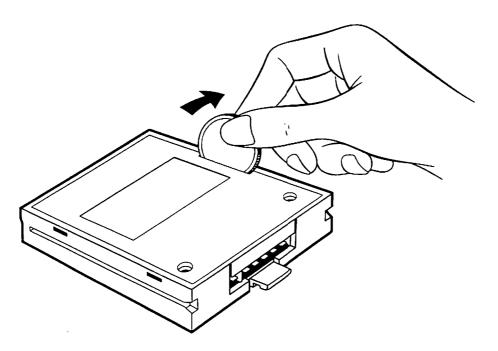

|         | 3.1 Inserting Cartridge (RAM, ROM)          | 6  |

|         | 3.2 Battery Installation                    | 7  |

|         |                                             |    |

| CHAPTER | OPERATION TEST                              |    |

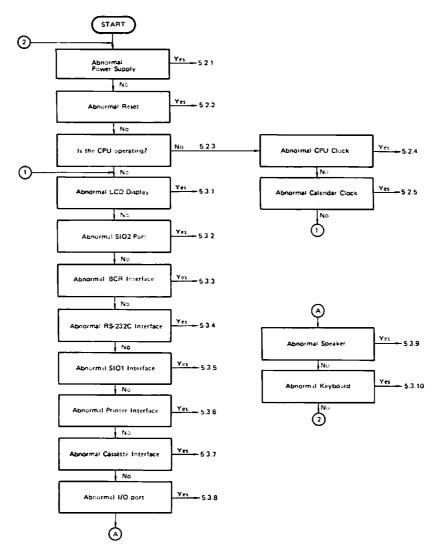

|         | 1 Operations Test Flow Chart                |    |

|         | 2 CPU Peripheral Circuit                    |    |

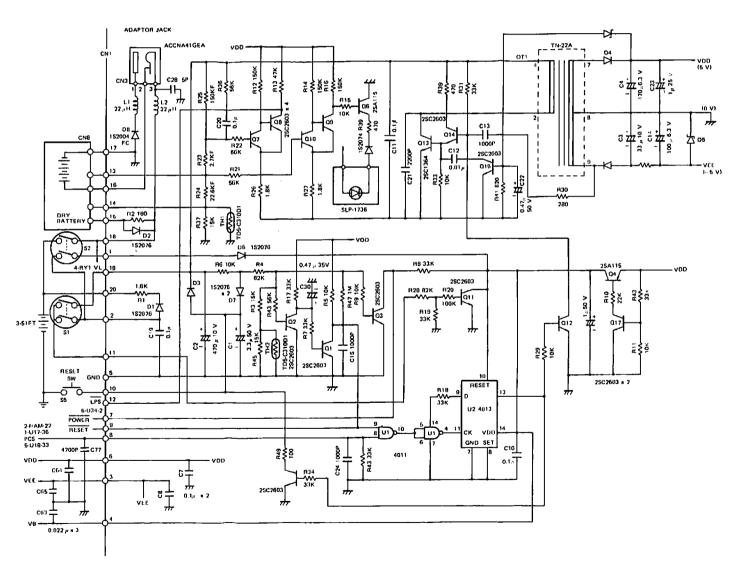

|         | 2.1 PC-8201 Power Supply Operation Test     |    |

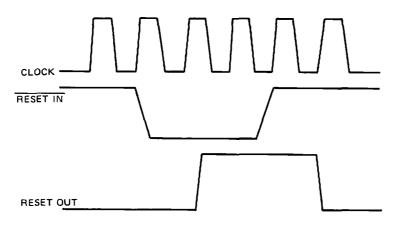

|         | 2.2 Reset Operation Test                    |    |

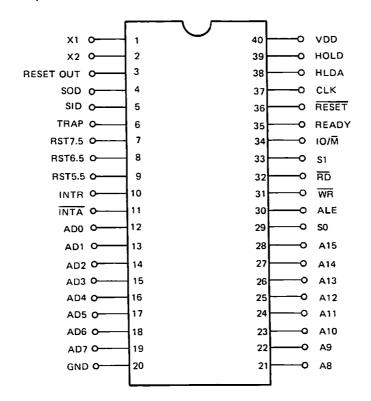

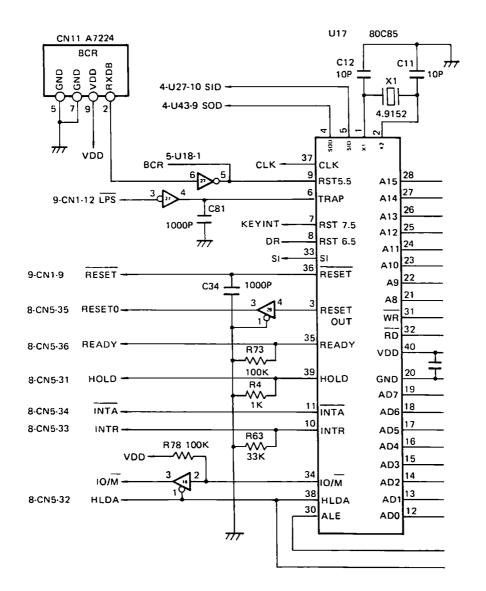

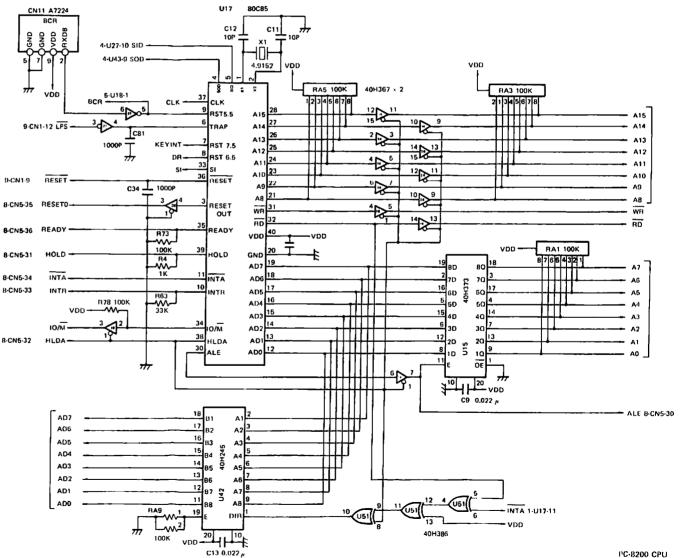

|         | 2.3 CPU (80C85) Operation Test              |    |

|         | 2.4 CPU Clock Operation Test                |    |

|         | 2.5 Calendar Clock Operation Test           |    |

|         | 3 1/O Peripheral Circuit                    |    |

|         | 3.1 LCD Operation Test                      |    |

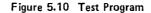

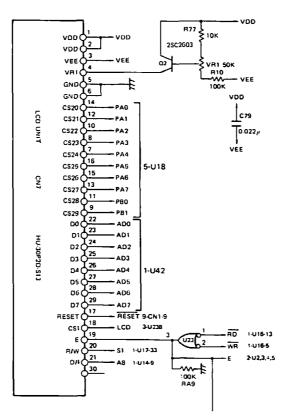

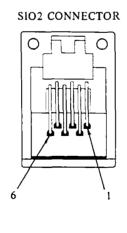

|         | 3.2 SIO2 Port Operation Test                |    |

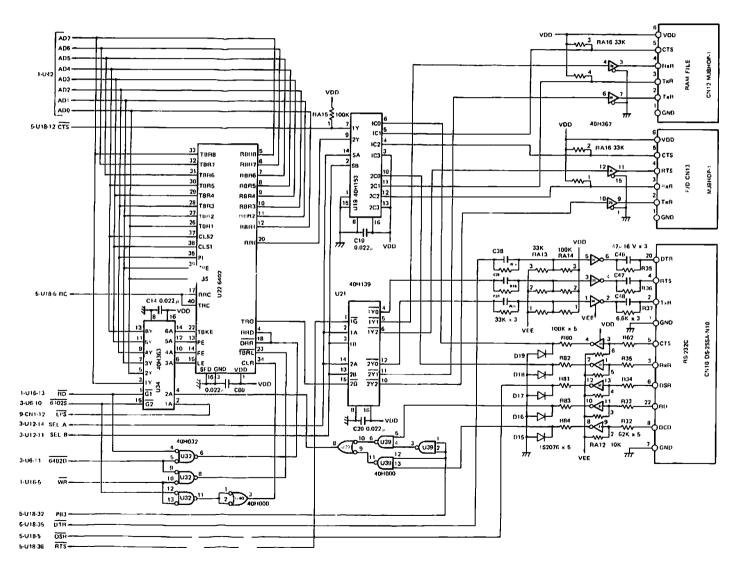

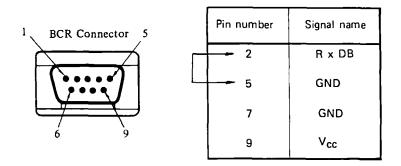

|         | 3.3 BCR Interface Operation Test            | 13 |

|         | 3.4 RS-232C Interface Operation Test        |    |

|         | 3.5 SIO1 Interface Operation Test           | 17 |

|         | 3.6 Printer Interface Operation Test        | 19 |

|         | 3.7 Audio Cassette Interface Operation Test | 21 |

|         | 3.8 I/O Port Operation Test                 | 27 |

|         | 3.9 Speaker Operation Test                  | 31 |

|         | 3.10 Keyboard Operation Test                | 31 |

|         |                                             |    |

| CHAPTER | TROUBLESHOOTING                             | _  |

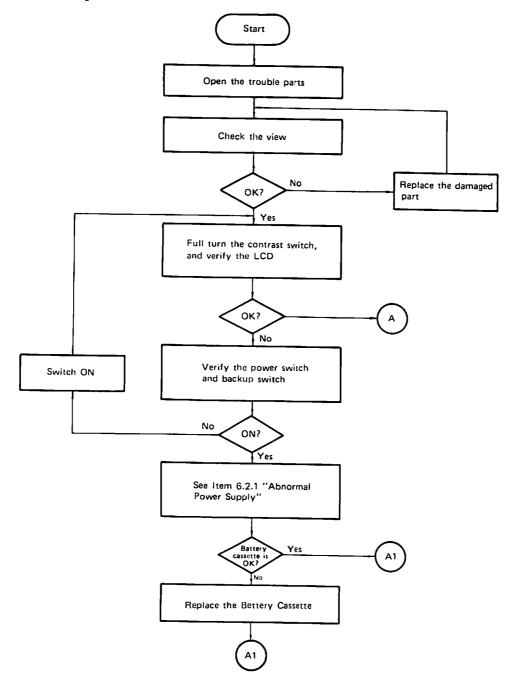

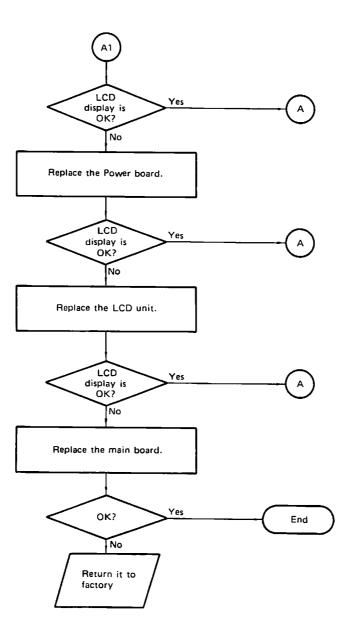

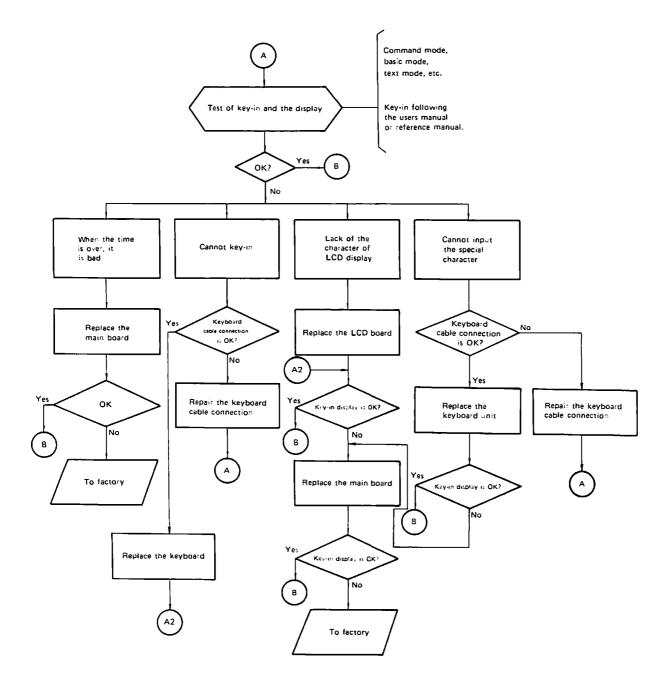

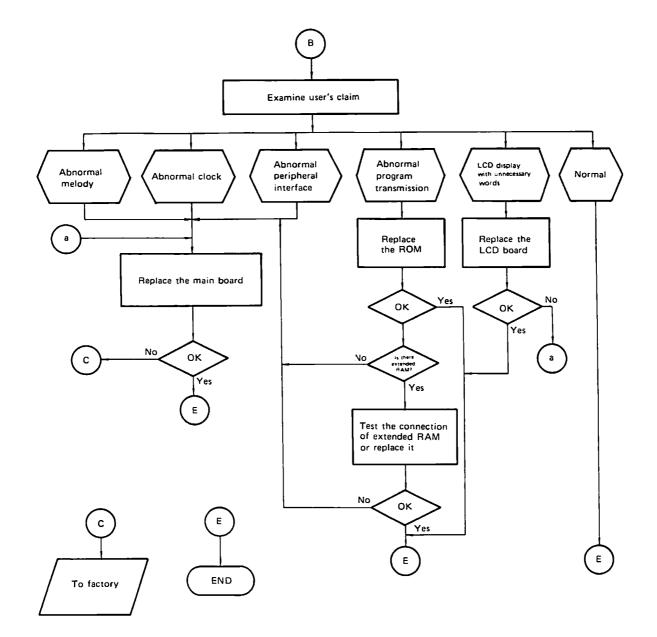

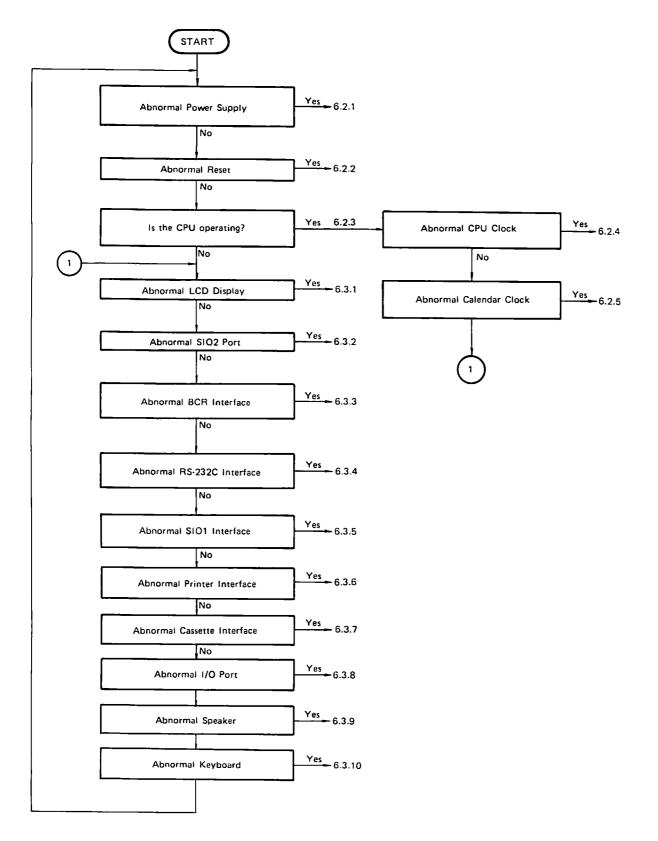

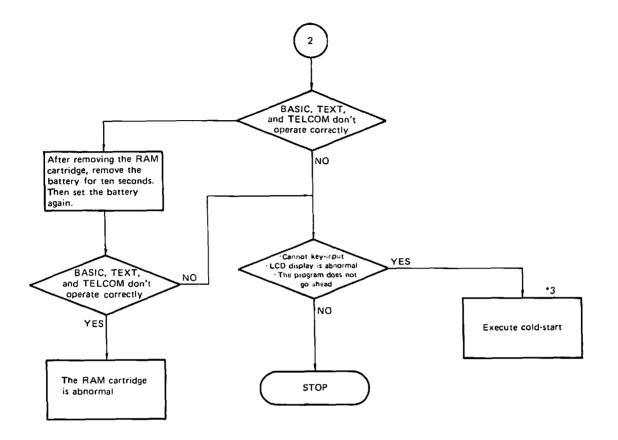

|         | 1 Troubleshooting Flowchart                 |    |

|         | 2 CPU Peripheral Circuit                    |    |

|         | .2.1 PC-8201 Abnormal Power Supply          |    |

|         | .2.2 PC-8201 Abnormal Reset                 |    |

|         | .2.3 PC-8201 Abnormal CPU (80C85)           |    |

|         | .2.4 Abnormal CPU Clock                     |    |

|         | .2.5 Abnormal Calendar Clock                |    |

|         | .3 I/O Peripheral Circuit                   |    |

|         | .3.1 Abnormal LCD Display                   |    |

|         | .3.2 Abnormal SIO2 Port                     |    |

|         | .3.3 Abnormal BCR Interface                 | -9 |

|         | .3.4 Abnormal RS-232C Interface             | 10 |

|         | .3.5 Abnormal SIO1 Interface                |    |

|         | .3.6 Abnormal Printer Interface             |    |

|         | .3.7 Abnormal Audio Cassette Interface      | 10 |

|         | .3.8 Abnormal I/O Port                      | 11 |

|         | .3.9 Abnormal Speaker                       | 12 |

| •       | .3.10 Abnormal Keyboard                     | 12 |

|         |                                             |    |

\*

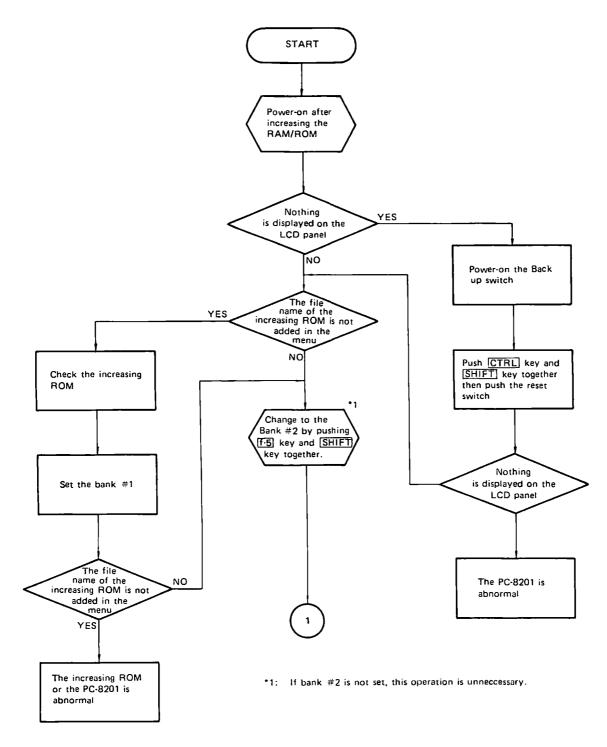

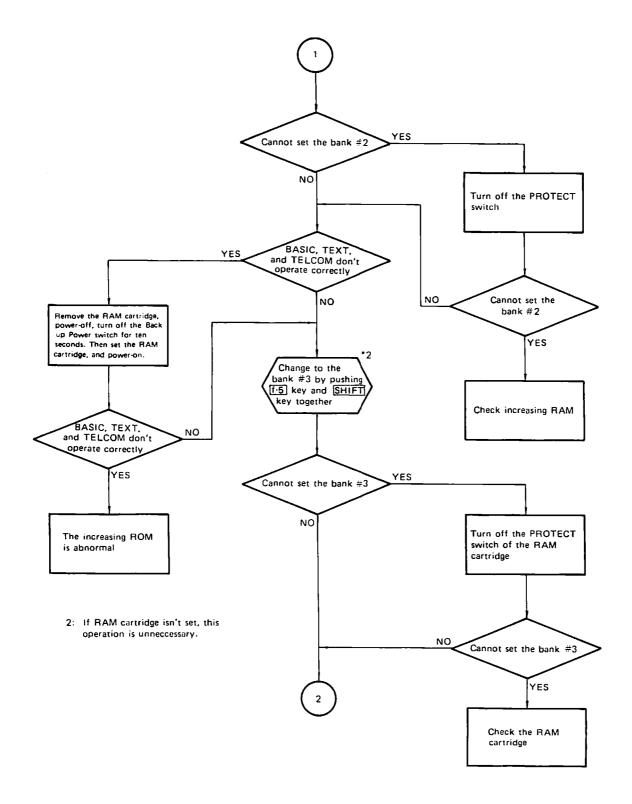

APPENDIX A OPERATIONAL MISTAKES

ŕ

-ii-

# APPENDIX B IC REMOVAL

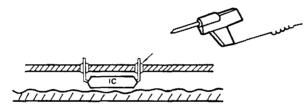

| B-1 | Necessary Equipment                     |

|-----|-----------------------------------------|

|     | ICs on Printed Circuit Board            |

| B-3 | ICs with Sockets                        |

| B-4 | Drawings of Insertion and Removal of IC |

# APPENDIX C PARTS LIST

APPENDIX D CIRCUIT DIAGRAM

APPENDIX E LSI DATA SHEET

an Marina Ang

.

ALL STRAT

# CHAPTER 1 INTRODUCTION

• •  $\langle \cdot \rangle$

٠

÷

### 1.1 Specifications

(1) Main Components

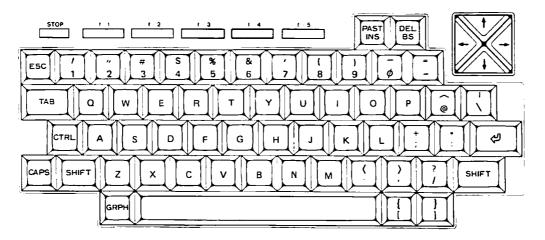

| a) | Keyboard<br>67 keys<br>Function keys:<br>Cursor lead keys:<br>Others:                                          | 5<br>4<br>58                                                                                                                      |

|----|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| b) | LCD<br>Effective display area:<br>Display panel:<br>Dot size:<br>Dot pitch:<br>Display characters:<br>Reverse: | 191.2(W) x 50.4(H) mm<br>240 x 64 full dot matrix<br>0.73 x 0.73 mm<br>0.8 mm<br>40 (characters) x 8 (rows)<br>By escape sequence |

| a  | Operation Potterica                                                                                            |                                                                                                                                   |

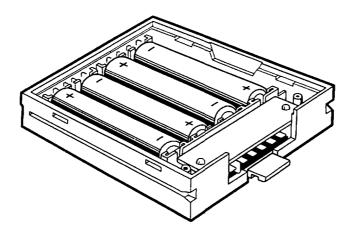

| c) | Operation Batteries<br>Batteries:                                                                              | Four time AA                                                                                                                      |

|    | Datteries:                                                                                                     | Four type AA                                                                                                                      |

|    | Operation times                                                                                                | Alkaline-manganese batteries<br>4.5 days                                                                                          |

|    | Operation time:                                                                                                | •                                                                                                                                 |

|    |                                                                                                                | (At four hours/day)<br>18 days                                                                                                    |

|    |                                                                                                                | (At one hour/day)                                                                                                                 |

|    |                                                                                                                | Note: With I/O disconnected                                                                                                       |

|    | Battery cassette:                                                                                              | $70(W) \times 80.5(D) \times 19(H) \text{ mm}$                                                                                    |

|    | Power OFF:                                                                                                     | Manual power off                                                                                                                  |

|    | Tower OTT.                                                                                                     | (It is possible to command in BASIC.)                                                                                             |

|    |                                                                                                                | (Variable minutes one to twenty-five min-                                                                                         |

|    |                                                                                                                | utes)                                                                                                                             |

|    | Low voltage display:                                                                                           | Light a LED                                                                                                                       |

|    |                                                                                                                | (Operate for more than twenty minutes after                                                                                       |

|    |                                                                                                                | lighting the LED.)                                                                                                                |

| d) | Memory Protection Battery (On                                                                                  | main PCB)                                                                                                                         |

| -, | Battery:                                                                                                       | Rechargeable battery                                                                                                              |

|    | Protection time:                                                                                               | About 26 days (16K bytes)                                                                                                         |

|    |                                                                                                                | About 7 days (14K bytes)                                                                                                          |

|    | Recharge method:                                                                                               | Trickle charge by AC adapter or operation                                                                                         |

batteries

|     | e)  | LSIs<br>CPU:<br>ROM:                                                                | 80C85<br>Code and pin compatible with 8085<br>Standard 32K bytes                                                                                                    |

|-----|-----|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |     | RAM:                                                                                | Option 32K bytes (connect a IC socket)<br>Standard 16K bytes<br>Option 16K bytes (connect a IC socket)<br>Option 32K bytes (connect a IC socket)                    |

|     |     | CLOCK:                                                                              | Option 32K bytes (connect a RAM cartridge)<br>2.4 MHz                                                                                                               |

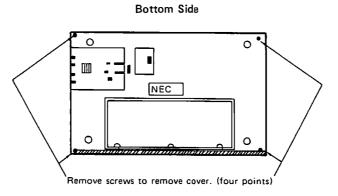

|     | ſ)  | Dimensions:                                                                         | Front;<br>300(W) × 215(D) × 35(H) mm<br>Back:<br>300(W) × 215(D) × 61(H) mm                                                                                         |

| (2) | I/O | interface                                                                           |                                                                                                                                                                     |

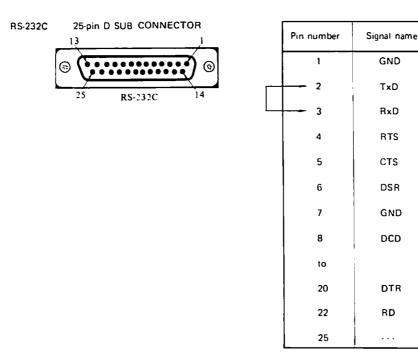

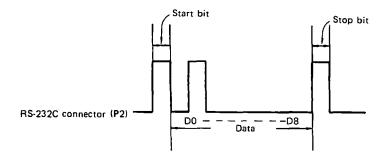

|     | a)  | RS-232C<br>Word length:<br>Parity:<br>Stop bit length:<br>Baud rate:                | 6.7 or 8 bits<br>Non, EVEN or ODD<br>1 or 2 bit<br>75, 110, 300, 600, 1200, 2400, 4800, 9600,<br>19200 BPS                                                          |

|     | b)  | SIO2<br>Distance of transfer:<br>Word length:<br>Baud rate:<br>Parity:<br>Stop bit: | 3 mMin.<br>8 bit<br>19200<br>Non<br>1 or 2 bit                                                                                                                      |

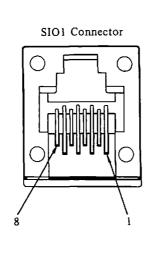

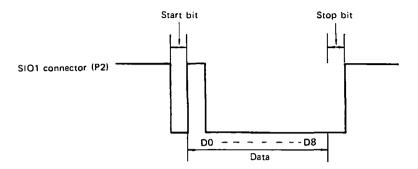

|     | c)  | SIO1<br>Distance of transfer:<br>Word length:<br>Baud rate:<br>Parity:<br>Stop bit: | 3 mMin.<br>8 bits<br>19200<br>Non<br>1 or 2 bit                                                                                                                     |

|     | d)  | CMT<br>Distance of transfer:<br>Baud rate:<br>File format:<br>Output level:         | <ul> <li>1.5 mMin.</li> <li>1200 or 600 (switchable by software control)</li> <li>Compatible with N-BASIC</li> <li>(binary file only)</li> <li>MIC level</li> </ul> |

|     | e)  | Printer:                                                                            | Conforms to Centronics Standards.                                                                                                                                   |

.

Ģ

. .

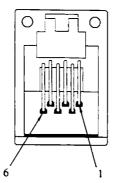

- f) BCR

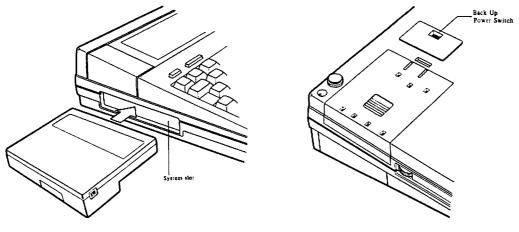

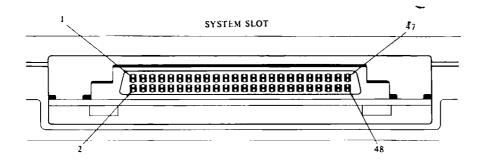

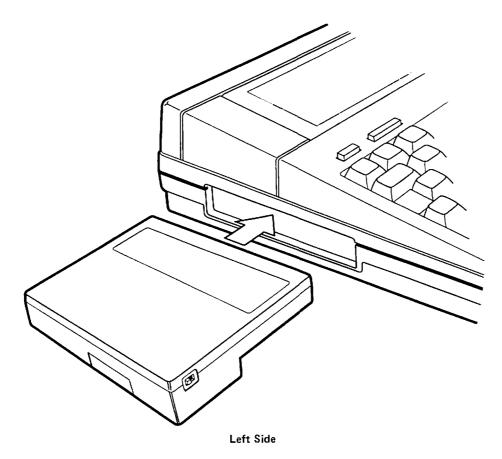

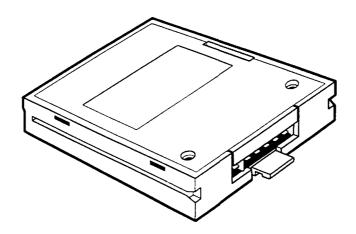

- g) System slot: For connecting a RAM cartridge.

#### 1.2 Switches and Contrast VR

(1) POWER Switch

Move this switch towards the rear to turn the power ON. To conserve the batteries, the PC-8201 automatically turns the power off if you do not use it for 10 minutes.

When an automatic power-off occurs, the switch will still be in the ON position even though the power is OFF.

To turn the power ON, move the switch to the OFF position, then back ON.

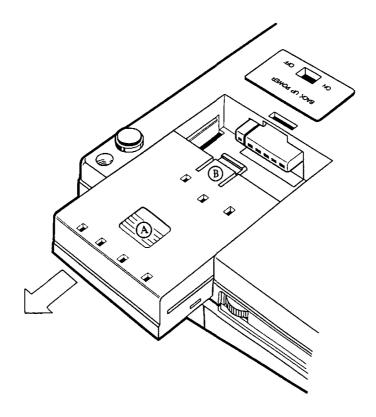

(2) BACK UP POWER Switch

This switch is for preventing discharge of the Ni-Cd battery for RAM back-up. The PC-8201A will not operate regardless of the setting of the power switch unless this switch is ON. Set this switch to OFF position if the PC-8201 is not to be used for a long time.

Note that the RAM will not be backed up when this switch is set to the OFF position.

(3) RESET Switch

If the PC-8201 "locks-up" (the display will "freeze" and all keys seem to be inoperative), press this button to return to the Main Menu (start-up) screen. It's highly unlikely that the PC-8201 will lock-up when you are using the built-in Application Programs.

However, this situation may occur with customized programs.

- (4) PROTECT Switch This switch is for protecting the contents of 2nd RAM. (BANK #2)

- (5) DISPLAY ADJUSTMENT DIAL This control is for adjusting the contrast of the LCD display relative to the viewing angle.

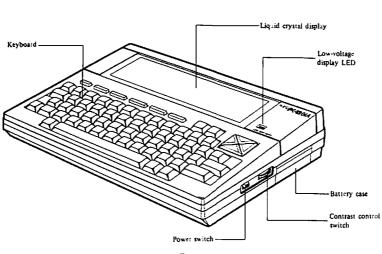

**CHAPTER 2**

**EXTERNAL VIEW**

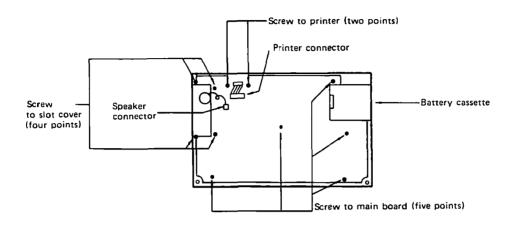

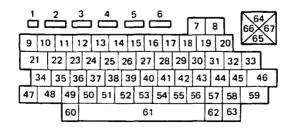

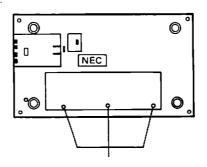

Front

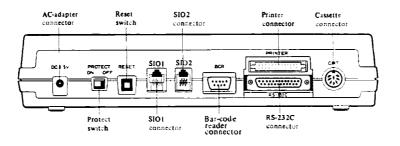

Back

Left Side

Rear View

$\langle \cdot \rangle$

۲

.

2-1/(2-2 blank)

•

# CHAPTER 3 FUNCTIONAL SPECIFICATIONS

#### 3.1 Logical Specifications

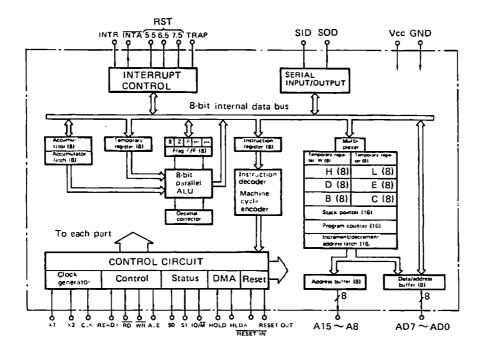

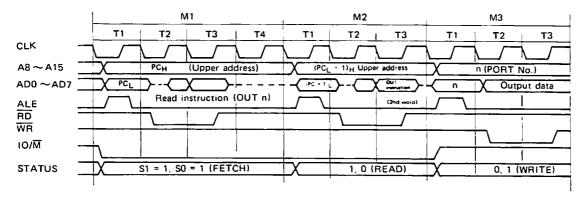

#### 3.1.1 CPU

- (1) Available CPU A 80C85 is used at 2.4 MHz.

- (2) How to Reset There are two kinds of reset: power on reset and manual reset. Pushing the reset switch initiates a warm-start; pushing it while pushing a shift-key and a control-key, initiates a cold-start.

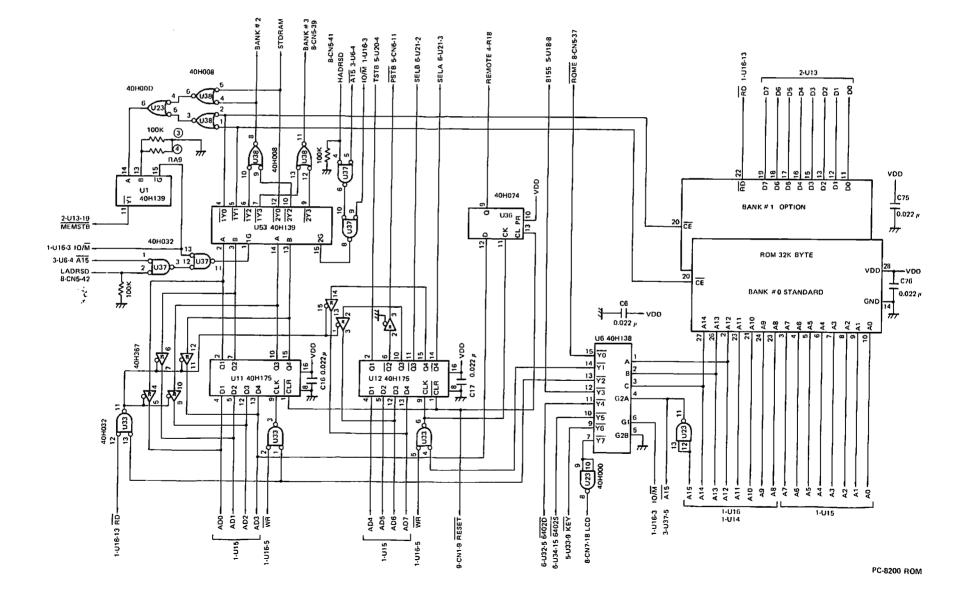

#### 3.1.2 ROM

- (1) Available ROM Available ROM is CMOS ROM, and the capacity is 32K byte. (#0)

- (2) User ROM A user ROM is 32K byte. The user ROM area is equipped with an IC socket which can be equipped with CMOS ROM. (#1)

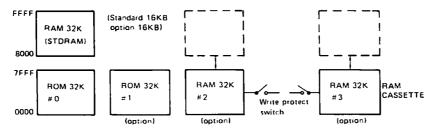

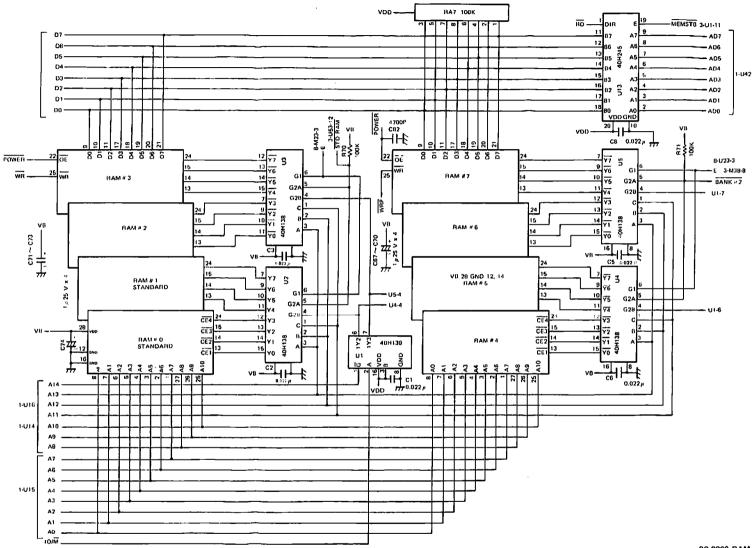

#### 3.1.3 RAM

(1) Available RAM

The eight 2K-byte CMOS ICs are used as RAM. The system comes with 16K bytes (STDRAM).

(2) Optional RAM

The PC-8201 is equipped with IC sockets for twenty-four 2K-byte CMOS ICs. 48K bytes. The first 16K bytes of this area are combined with the standard 16K byte RAM to make a 32K byte RAM area. The remaining 32K bytes, become RAM #2. There is also a 32K-byte RAM cassette (#3) port for external memory. It can be connected with a system bus output in PC.

Memory Configuration

Optional RAM #2 and RAM cassette #3 have write protect switches, and they can select the address (0 to 7FFF or 8000 to FFFF) by software control. Memory is controlled at the following I/O port.

×.

Ļ

.

|        | 1010 000 | O 1 OUT A1H                                                                         |

|--------|----------|-------------------------------------------------------------------------------------|

|        |          | 3     2     1     0       HADR     HADR     LADR     LADR       2     1     2     1 |

| LADR 2 | LADR 1   | SELECT ADDRESS (0H to 7FFFH)                                                        |

| 0      | 0        | BANK #0 (ROM #0)                                                                    |

| 0      | 1        | BANK #1 (ROM #1)                                                                    |

| 1      | 0        | BANK #2 (RAM #2)                                                                    |

| 1      | 1        | BANK #3 (RAM #3)                                                                    |

| HADR 2 | HADR 1   | SELECT ADDRESS (8000H to FFFFH)                                                     |

| 0      | 0        | STANDARD ROM                                                                        |

| 0      | 1        | NOT USED                                                                            |

| 1      | 0        | BANK #2 (RAM #2)                                                                    |

| 1      | 1        | BANK #3 (RAM #2)                                                                    |

-6

3 - 2

# 3.1.4 LCD Interface

| (1) |                         | B (Ten)                                 |                                    |             | RAM 200 by  | /te           | ×              |

|-----|-------------------------|-----------------------------------------|------------------------------------|-------------|-------------|---------------|----------------|

| (2) | Available LC<br>LR-202C | CD                                      |                                    | Number      | of dots     | 240 x 64      |                |

| (3) |                         |                                         | ows                                |             |             |               |                |

|     | *2* Config<br>Both a    |                                         |                                    | and graphic | characters  | can be disp   | layed.         |

|     |                         | the comma                               | I/O port<br>and to LCD<br>from LCD |             |             |               |                |

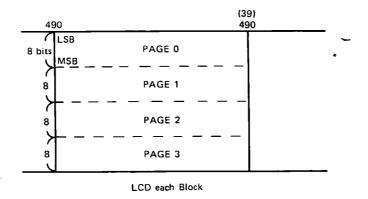

|     | Т                       | isplay On/C<br>he LCD is<br>splayed sep | divided int                        | o the follo | wing IC blo | ocks. Eacl    | h block can be |

|     | ſ                       | B1                                      | B2                                 | B3          | B4          | <sub>85</sub> |                |

|     | 14 dots -               | - — — — †<br>86                         | <br>B7                             | — <u> </u>  |             | B10           | -              |

|     | Ą                       | I                                       |                                    | 240 dots    | ·           |               | ł              |

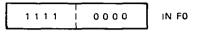

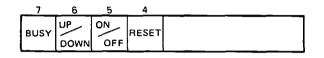

|     |                         | 1 1 1 1                                 | 0 0 0 0                            |             |             |               |                |

| O   |                         |                                         |                                    |             |             |               |                |

|     |                         | 0                                       | 0 1                                | 1 1         | 0 0         | DISP          |                |